数字逻辑复习

期末的小小总结

[TOC]

PPT查看与下载

第一章 数字逻辑电路基础

两类信号:模拟信号,数字信号。

时间和幅值均连续,模拟信号。时间和幅值均离散,数字信号。

处理数字信号的电路叫做数字电路。

几种简单编码

BCD码

8421码, 5421码,2421码, 余三码。

有权BCD码:8421码, 5421码,2421码。

5421BCD码和2421BCD码不唯一。

5421BCD码前五个码和后五个码一一对应,仅高位不同。

2421BCD码后五个码以中心对称去反,这样的代码成为自反代码。4和5互为反码,3和6,… 0和9互为反码。

余三码是无权BCD码,是在8421BCD码的基础上加上0011(3)形成的编码。每位数码无确定的位权。

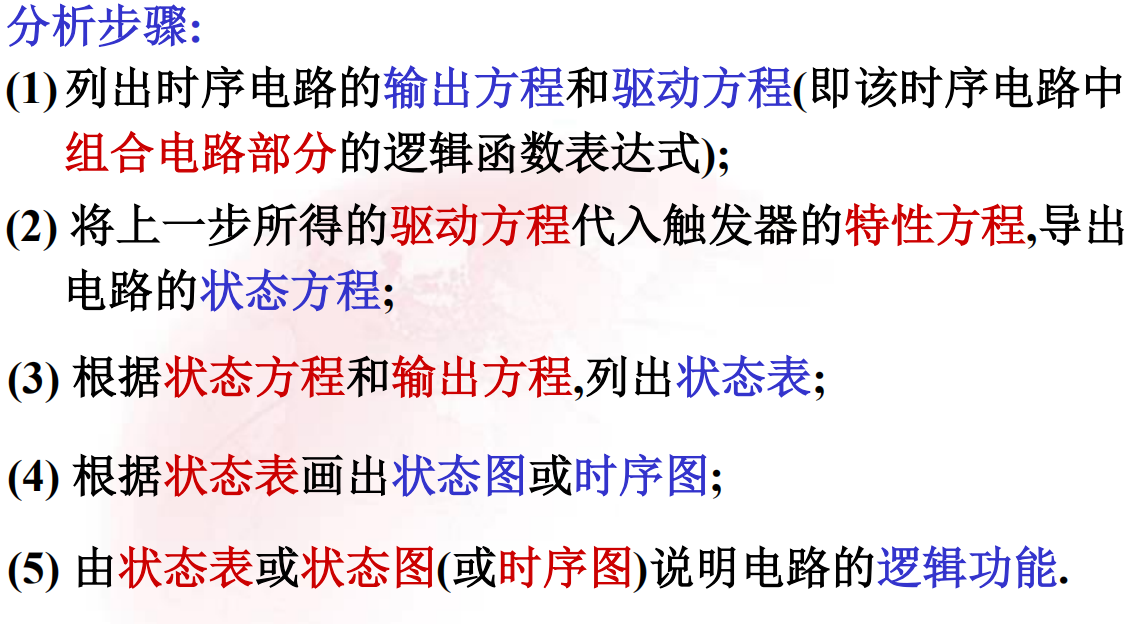

格雷码

格雷码是循环码。

image-20211224115406876

奇偶校验码

具有检错能力的代码

奇校验:原代码的基础上加上一个码位使得代码中含有1的个数为奇数。

偶校验:原代码的基础上加上一个码位使得代码中含有1的个数为偶数。

通过检查代码中含有的1的奇偶性来判断代码的合法性。

字符数字码

ASCII码等

算术运算

有符号数的表示方法

原码,反码,补码。

一个正数和比他小的负数相加,多出符号位的进位忽略。

两个负数相加,多出符号位的进位忽略。

逻辑运算

研究数字电路的基础是逻辑代数,也称布尔代数。

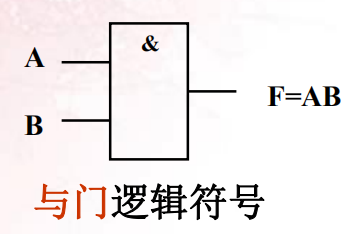

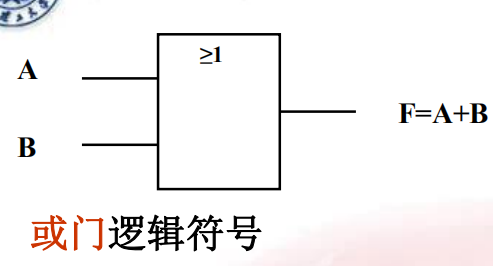

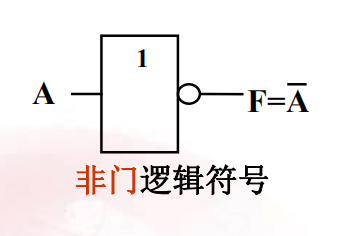

基本逻辑运算

逻辑代数中只有三种基本逻辑运算,即“与或非”。

image-20211224123044422 image-20211224123111238 image-20211224123130209

与门和或门可以有多个输入端。

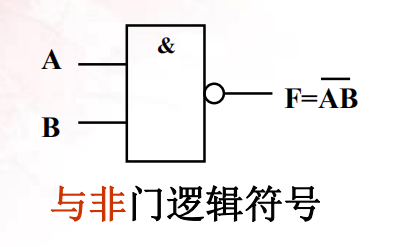

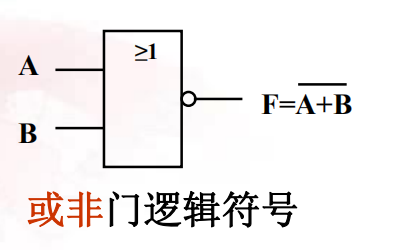

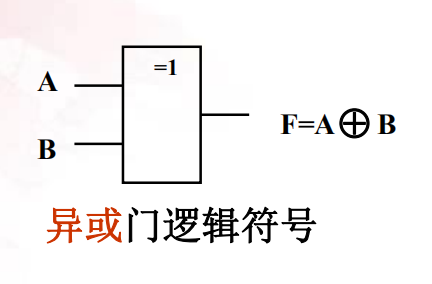

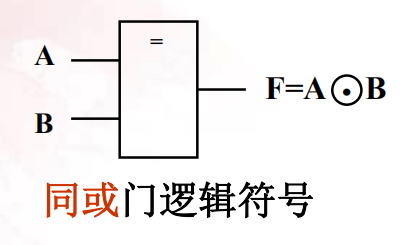

复合逻辑运算

image-20211224123244118 image-20211224123251089 image-20211224123349224 image-20211224123356545

同或和异或互为反函数。

正逻辑和负逻辑

正逻辑:高电平有效。

负逻辑:低电平有效。

逻辑代数的基本定律和规则

逻辑函数的相等

如果两个函数的真值表相等,则这两个函数一定相等。

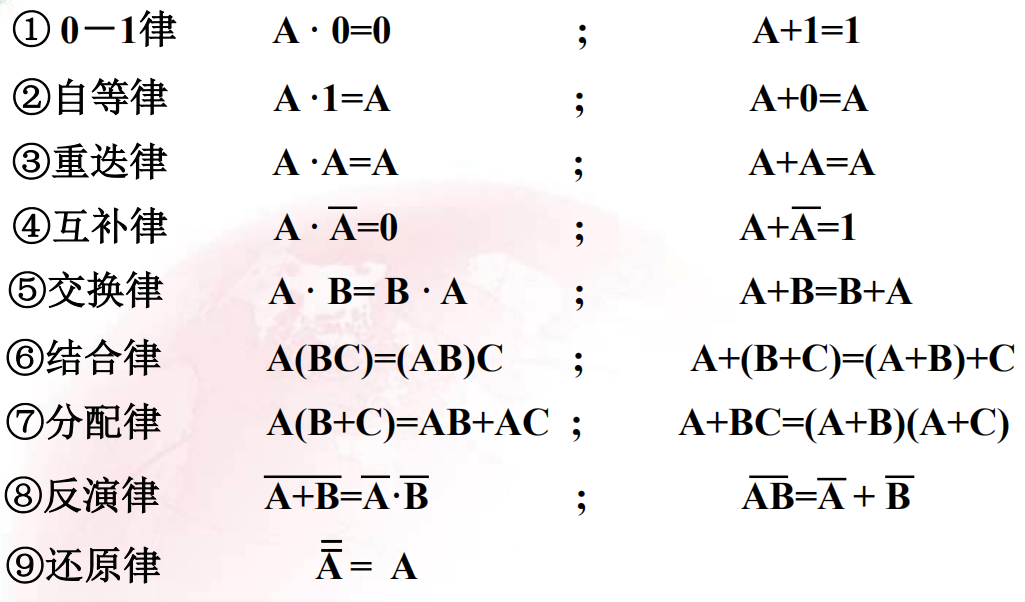

基本定律

逻辑代数的三条规则

代入规则。将一个等式中的某一变量使用一个逻辑函数式F代替,则等式仍然成立。

由1可证明反演律对n个变量仍然适用。

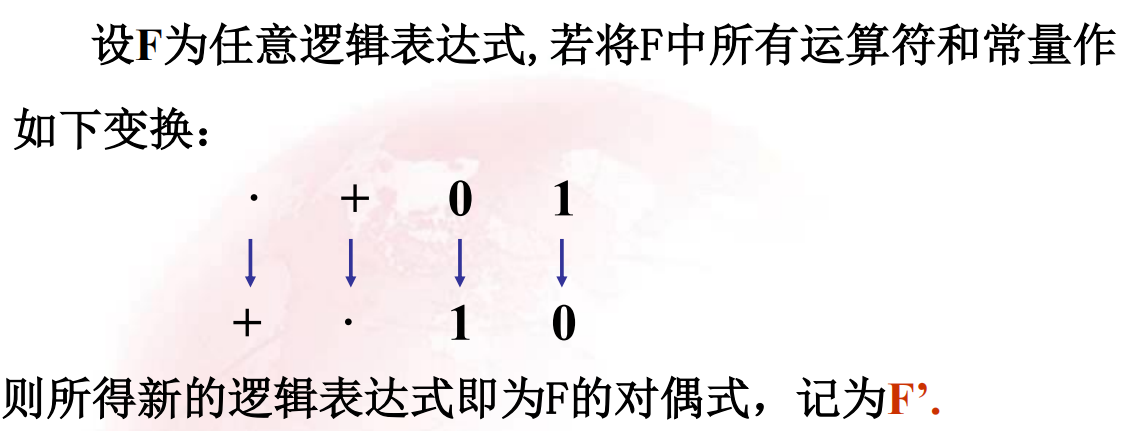

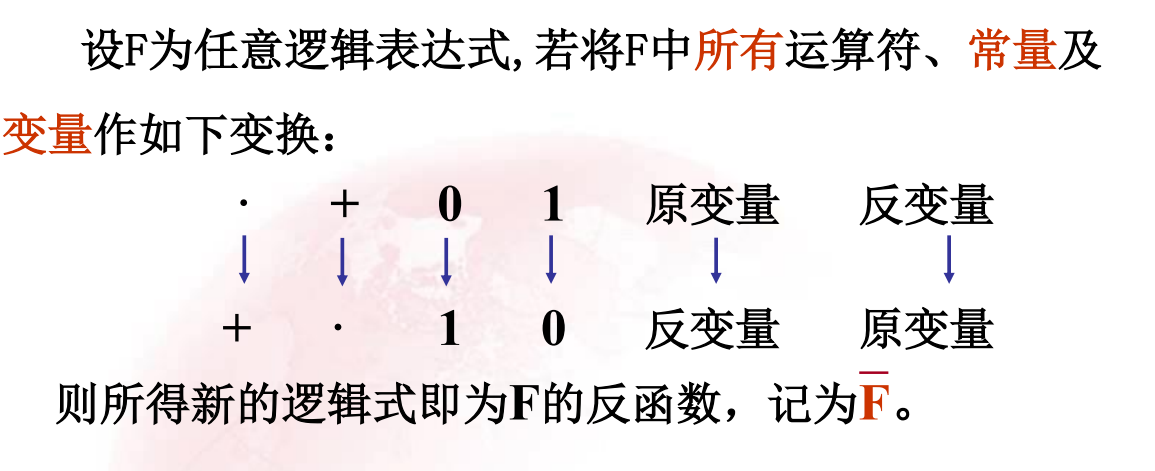

反演规则。

image-20211224124225032

注意:1.要保持原式的优先顺序。2.原式中不属于单变量上的非号不变。对偶规则。

注意:1.要保持原式的优先顺序。2.原式中的长短非号不变。3.单变量的对偶式为自己

对偶规则:若有两个逻辑表达式F和G相等,则各自的对偶式F’和G’也相等。

逻辑代数的常用公式

image-20211224125048354 image-20211224125051852

image-20211224125057158 image-20211224125100070

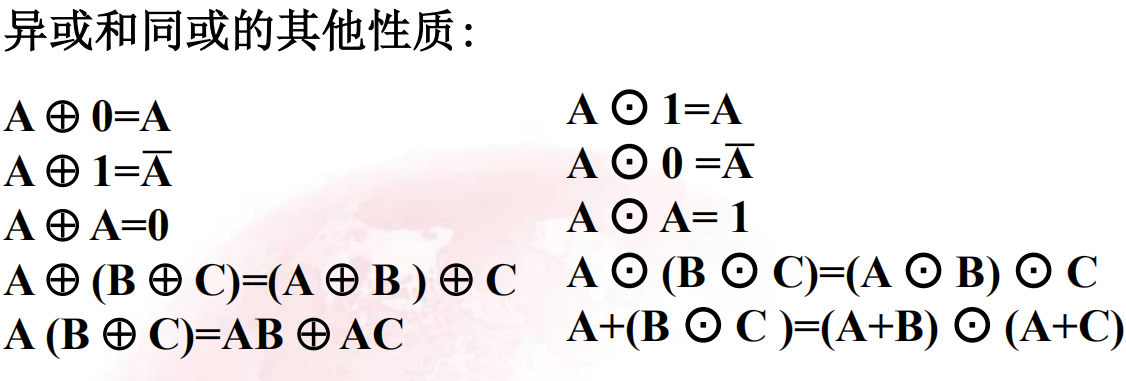

同或和异或:

偶数个变量:同或和异或互为反函数。

奇数个变量:同或和异或相等。

同或功能常常使用异或门来实现。

逻辑函数的标准形式

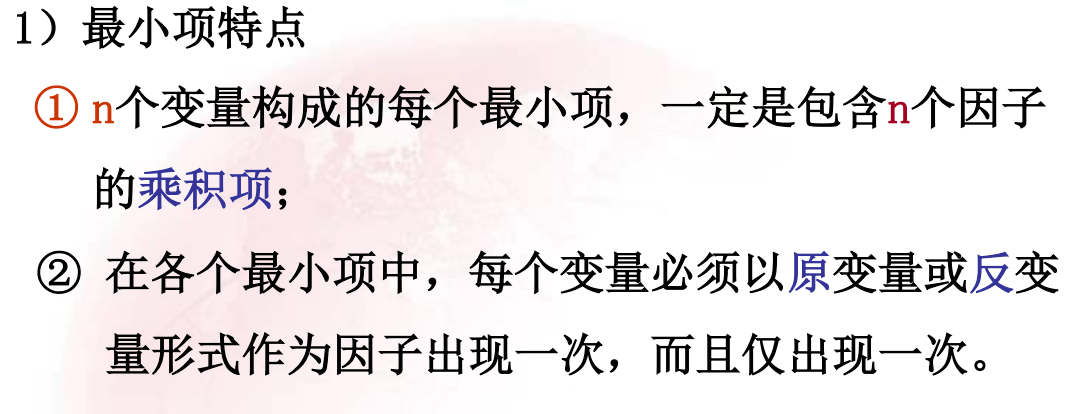

最小项和最大项

2)最小项编号:使该最小项的值为1所对应的等效十进制数。

3)最小项的性质:

- 变量任取一组值,仅有一个最小项为1,其他最小项为0;

- n变量的全体最小项之和为1

- 不同的最小项相与,结果为0

- 两最小项相邻,相邻最小项相“或”,可以合并成一 项,并可以消去一个变量因子。

- 已知F的最小项式,则F反的最小项式为F最小项的补集。F对偶式的最小项是F反中和2的n次方减1互补的那一项的值。

- 已知F的最小项式,则F的最大项的值为F最小项的补集。

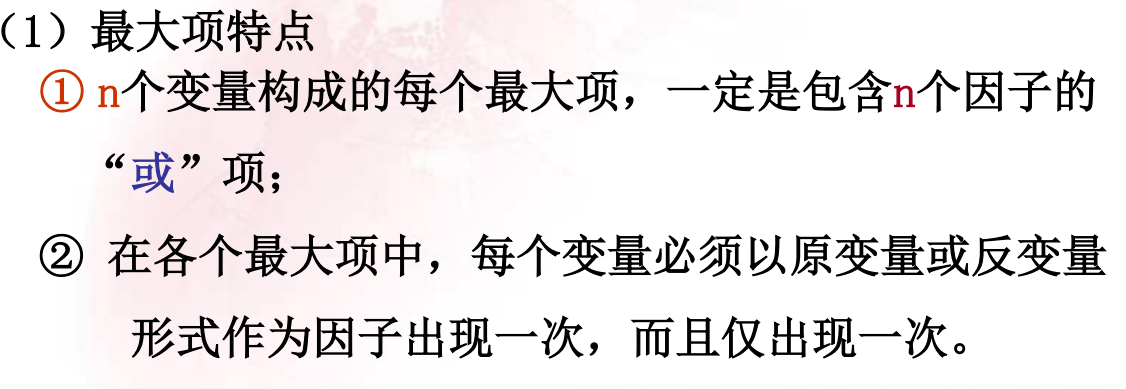

2)最大项编号:使该最小项的值为0所对应的等效十进制数。

3)最大项的性质:

- 变量任取一组值,仅有一个最大项为0,其它最大项为1

- n变量的全体最大项之积为0

- 不同的最大项相或,结果为1

- 两相邻的最大项相“与”,可以合并成一项,并可以消去一个变量因子

编号下标相同的最小项和最大项互为反函数。

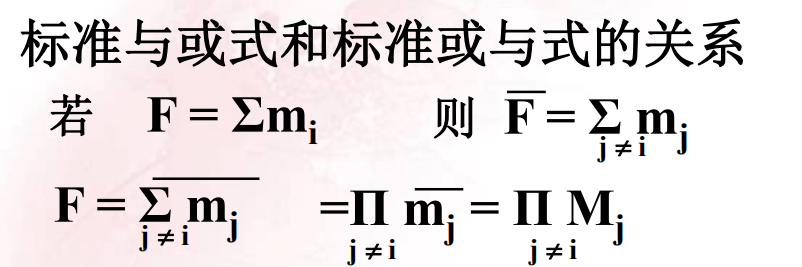

标准与或式和标准或与式

任一逻辑函数都可以表达为最小项之和的形式,而且是唯一的

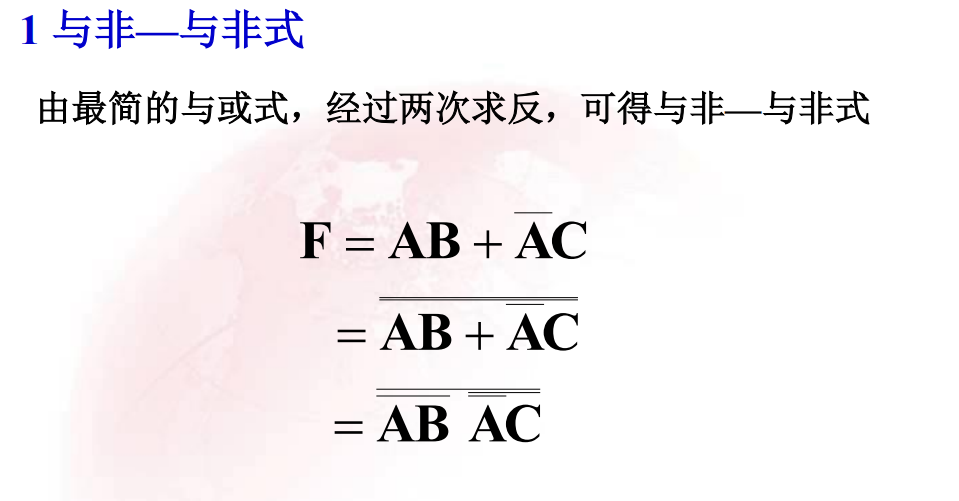

逻辑函数式化简为其它形式

可能会用来解决用特定的门电路来绘制电路图的问题。

比如与非门。

逻辑函数式与真值表

化为最小项之和的形式,最小项对应的为1。

逻辑函数的化简

卡诺图化简法

相邻的2的n次方的项进行合并,从相邻数最少的那个开始。每一次合并可以消去n个变量。

圈和圈可以重叠。

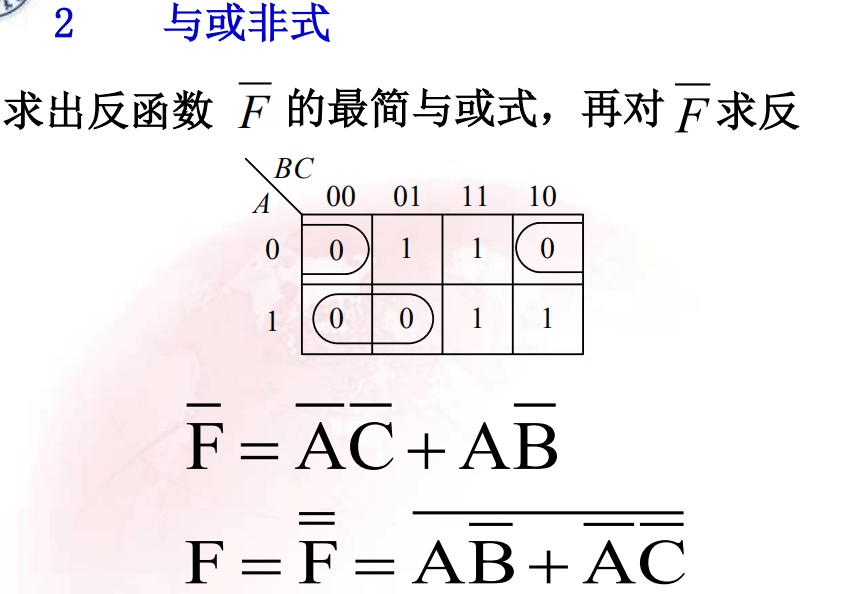

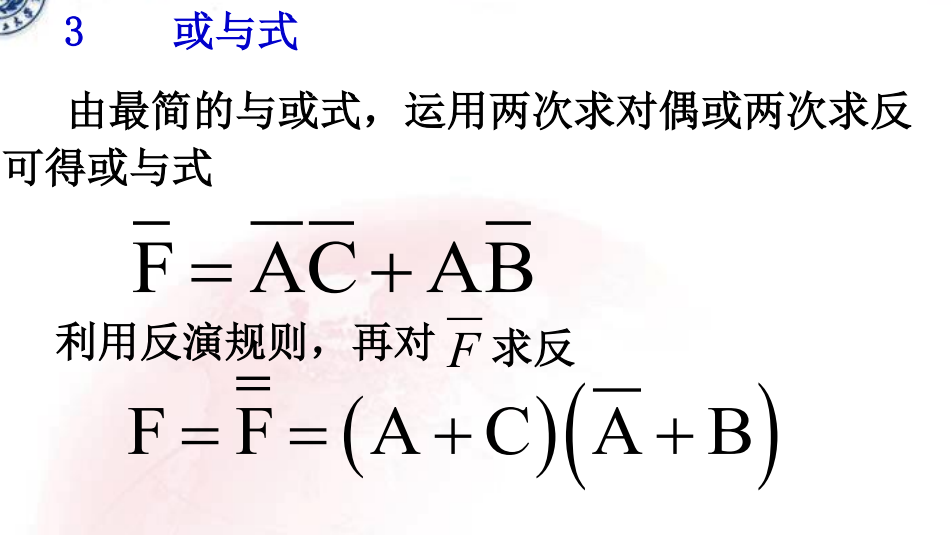

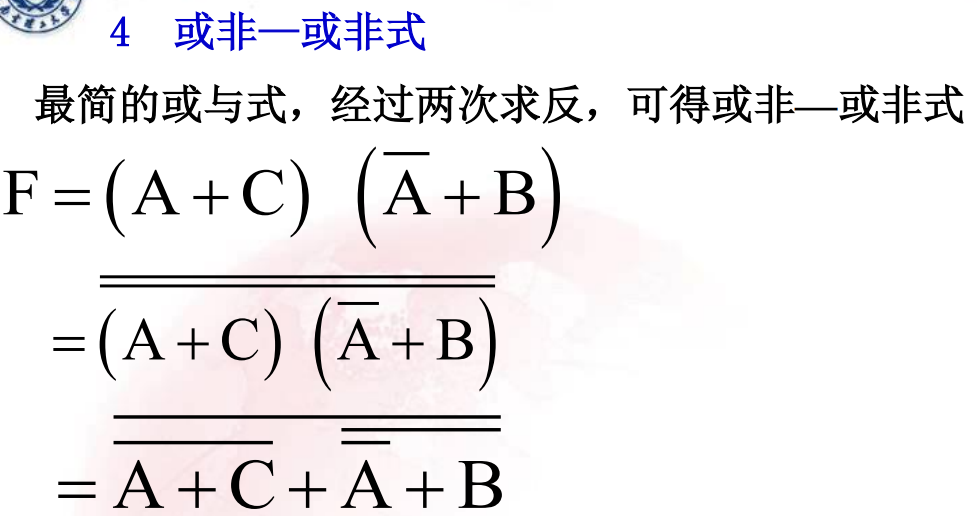

用卡诺图求反函数的最简与或式

合并卡诺图中的0方格。

可以用来求最简与或非式。

不完全确定的逻辑函数及其化简

无关项看为1,然后进行化简,但是在最后写的时候记得写无关项恒等的条件。

第二章 逻辑门电路

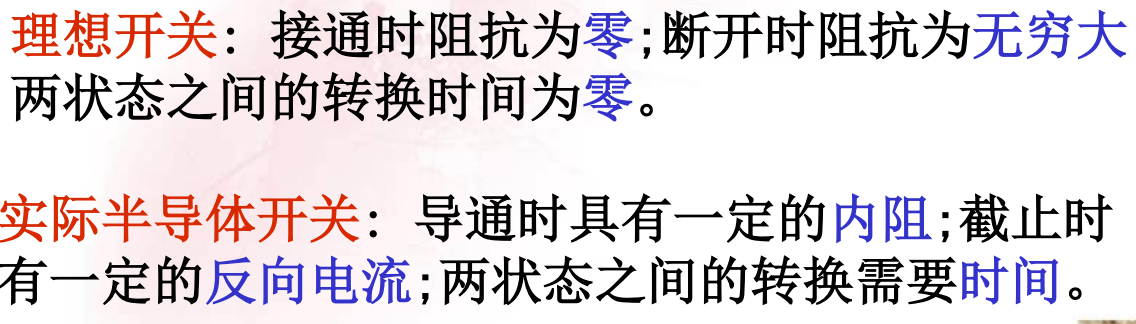

晶体管的开关特性

在数字电路中,常将半导体二极管,三极管和场效应管作为开关元件使用。

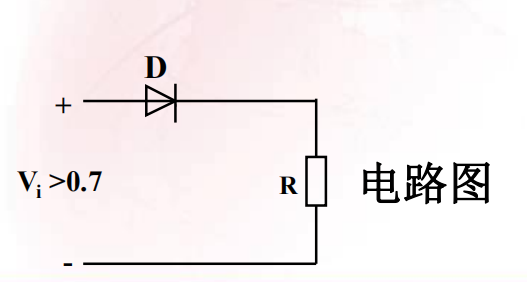

半导体二极管的开关特性

硅二极管的导通条件及导通时的特点:

大于0.7V导通,小于0.5V截止。

image-20211224153335271 image-20211224152809302

硅二极管的开启和关断时间都很小。

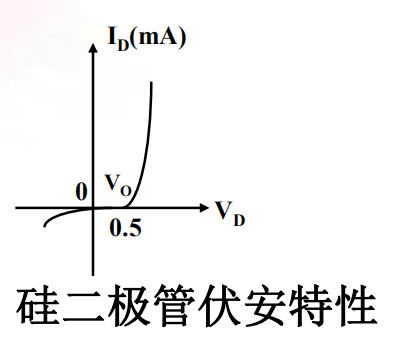

半导体三极管的开关特性

image-20211224153440538 image-20211224153739327

开关时间和导通的深度成正比。

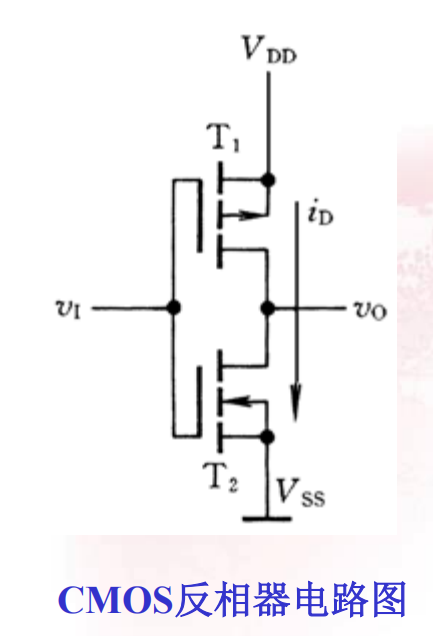

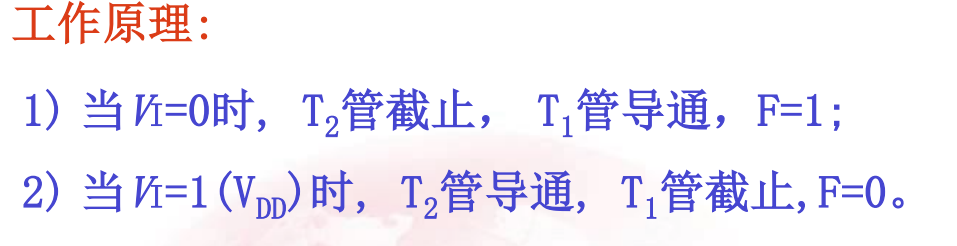

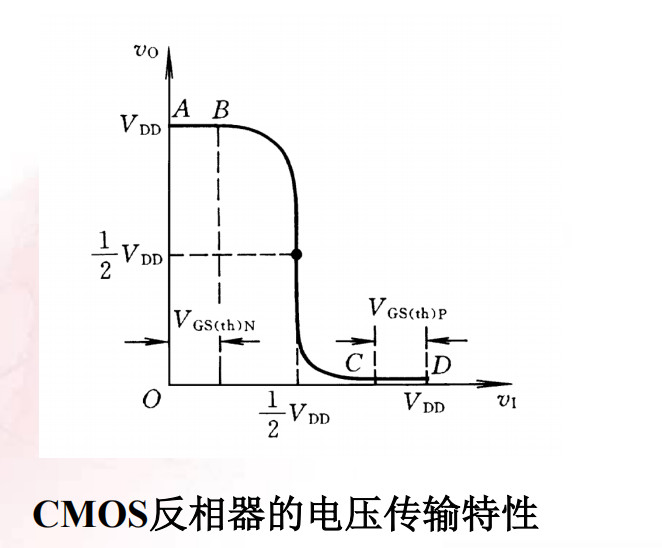

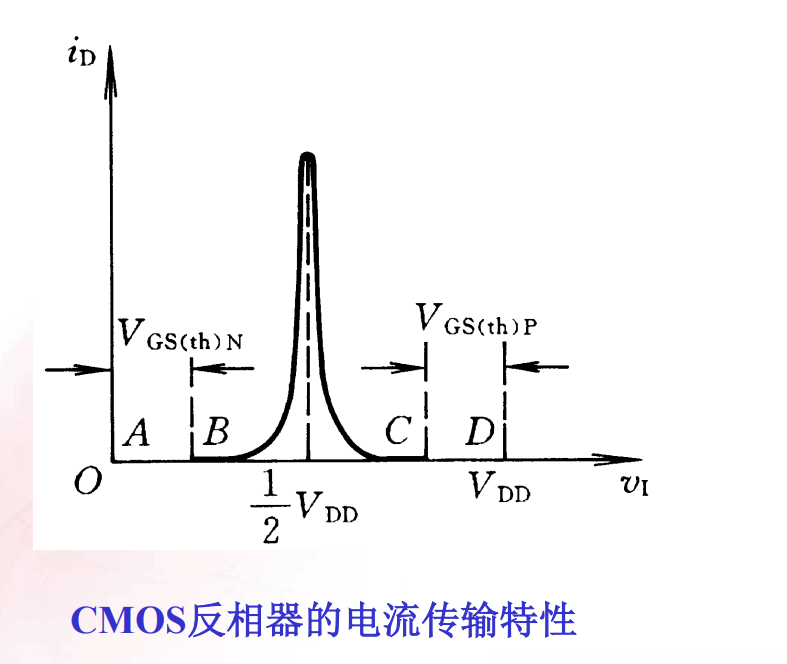

CMOS门电路

CMOS反相器:静态功率极小。

image-20211224154134084 image-20211224154143838

image-20211224154157789

image-20211224154228489

本质上就是一个非门。

第三章 组合逻辑电路

组合逻辑电路:电路在任一时刻的输出状态仅由该时刻的输入信号决定,与电路在此信号输入之前的状态无关

组合逻辑电路的分析

分析方法

分析步骤:

- 通过电路图写出逻辑函数表达式

- 通过逻辑函数表达式列出真值表。

- 通过真值表或者表达式分析电路的功能。

组合逻辑电路的设计

设计方法

设计步骤:

- 由实际逻辑问题列出真值表

- 由真值表写出逻辑表达式

- 化简,变换输出表达式。

- 画出逻辑图。

组合逻辑电路中的冒险

产生冒险的原因

由于门电路延迟时间的关系,可能会使逻辑电路产生错误输出。通常把这种现象称为竞争冒险。

电路存在由非门产生的互补信号,且互补信号的状态发生变化时有可能出现冒险现象。

消去冒险的方法

- 发现并消除互补变量

- 增加乘积项

第四章 常用组合逻辑功能器件

中规模集成电路分别具有特定的逻辑功能,称为功能模块。

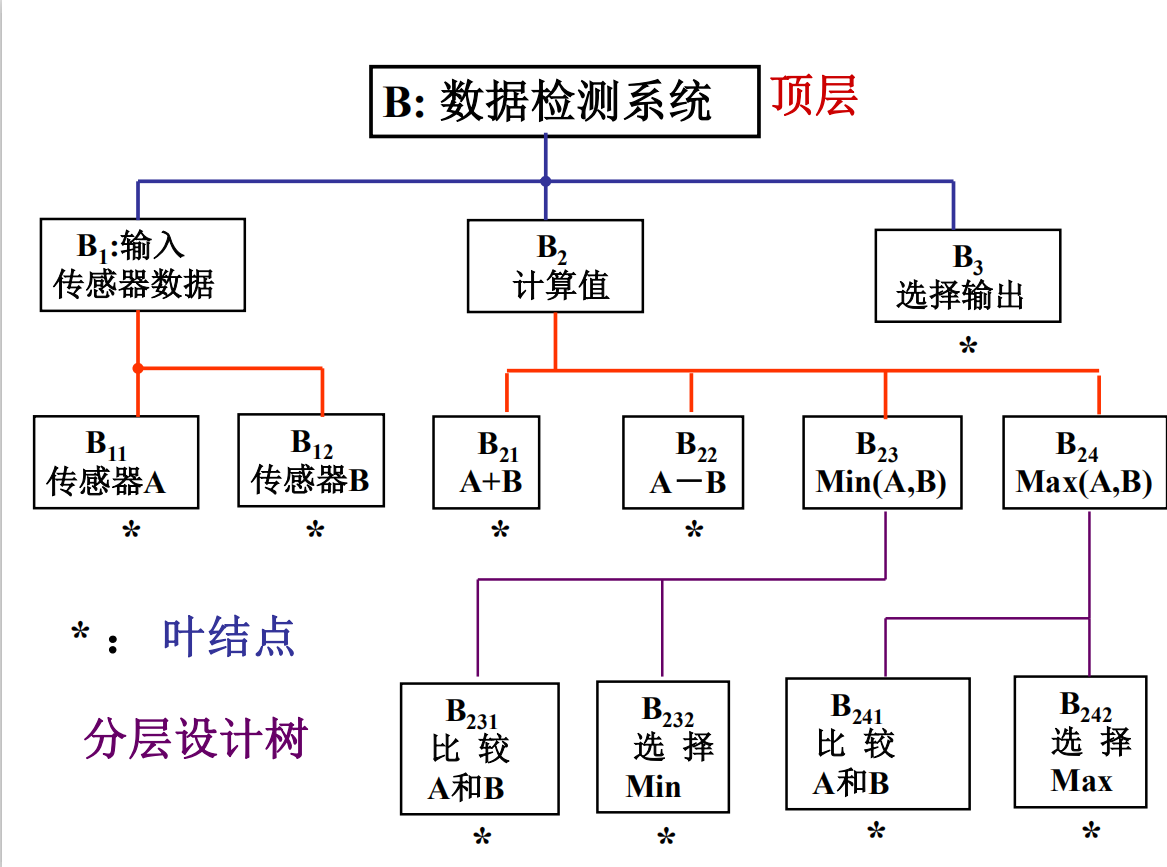

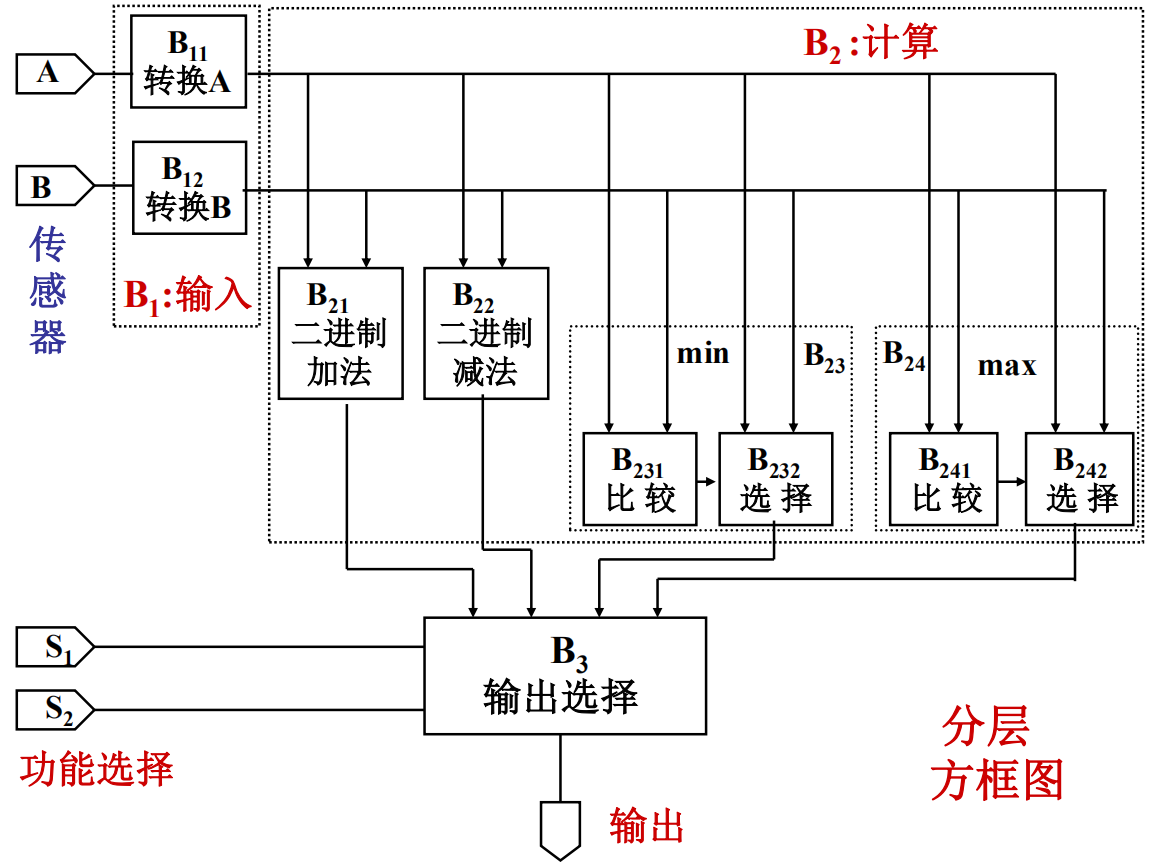

自顶向下的模块化设计方法

分层设计树

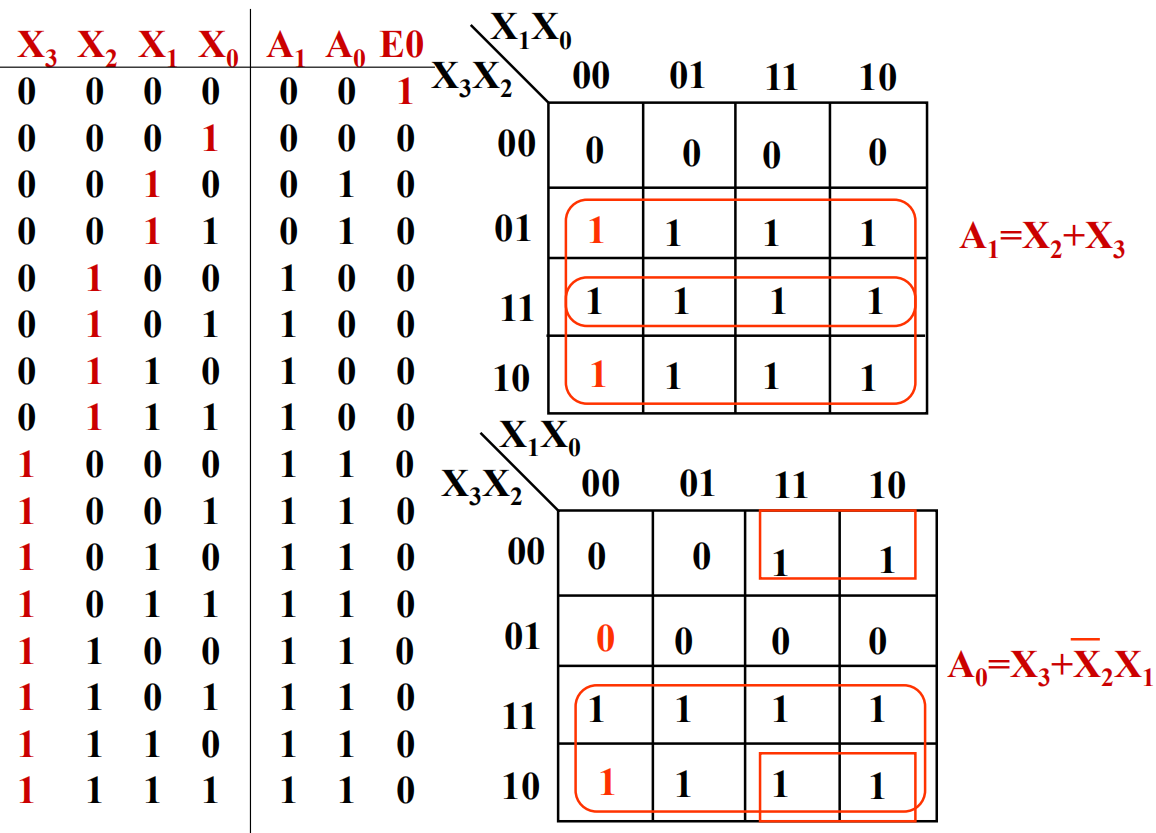

编码器

将信息(如数和字符等)转换成符合一定规则的二进制代码

二进制编码器

用n位二进制代码对N=2的n次方个特定信息进行编码的逻辑电路。

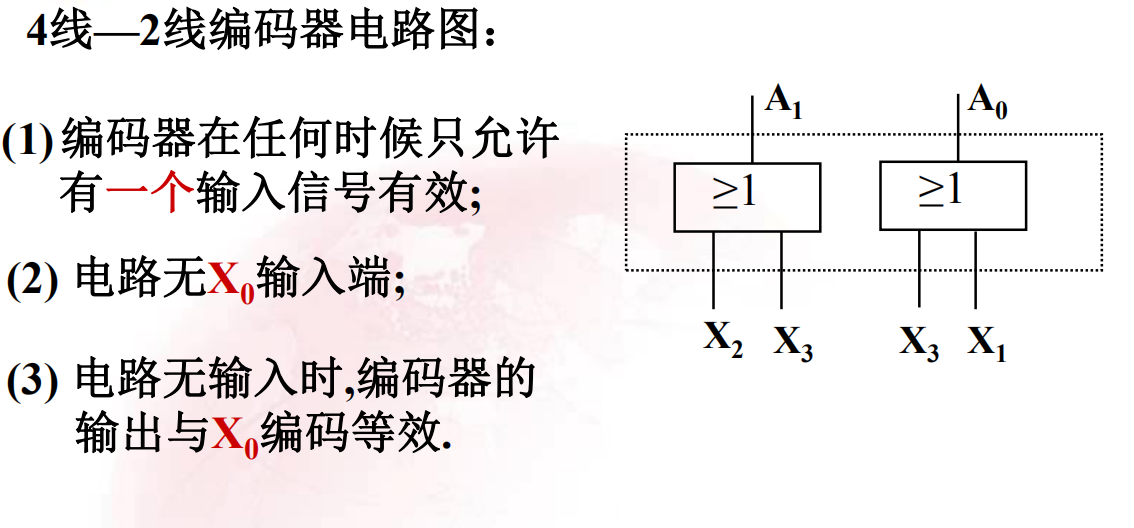

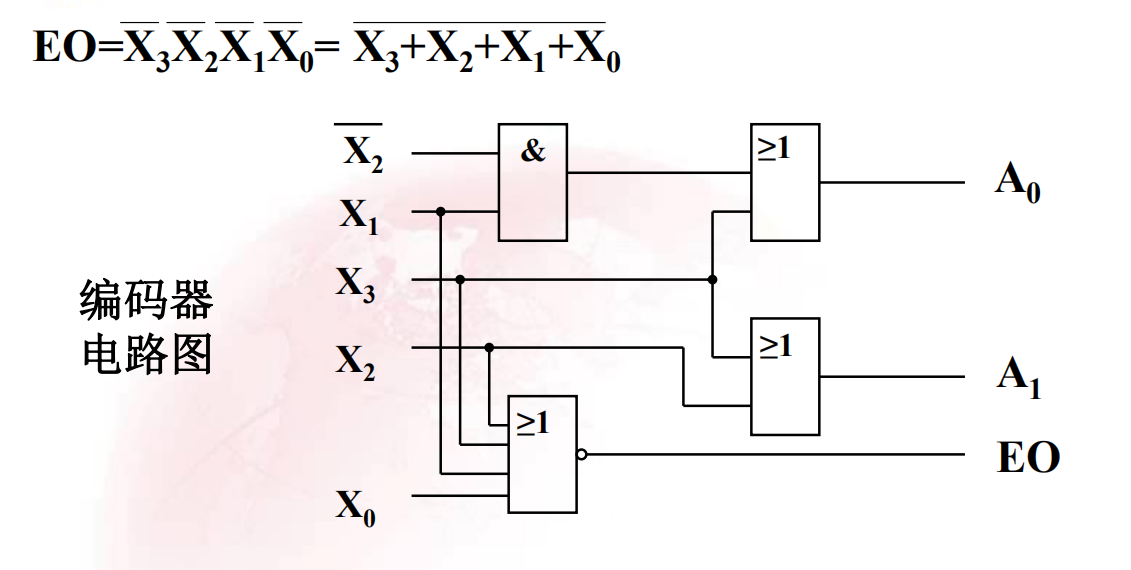

4线 — 2线编码器(将四个信息编码为一个2位二进制数)(4线中只允许有一个输入有效)

带输出使能端的优先编码器

输出使能端: 用于判别电路是否有信号输入(是一个输出信号,当没有任何信号输入时输出1,否则输出0)

优先: 对输入信号按轻重缓急排序,当有多个信号同时输入时,只对优先权高的一个信号进行编码.

该编码器所对应的真值表和逻辑电路图: image-20211224160457427

二 — 十进制编码器

输入: I0 ,I1,I2 … …I9,表示十个要求编码的信号.

输出: BCD码.

电路有十根输入线,四根输出线,常称为10线—4线编码器

通用编码器集成电路

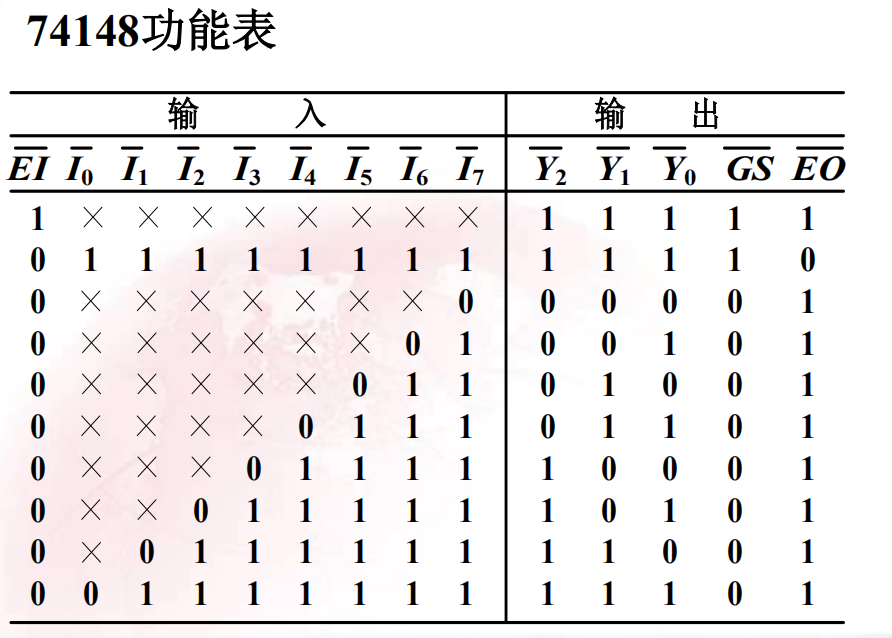

8线—3线优先编码器74148

1)74148为8线—3线优先编码器,HPRI是最高位优先编码器的说明。

2)编码器输入为低电平有效,输出为3位二进制反码。

3)EI非表示输入使能端,当EI非为0时电路正常工作,反之则电路禁止工作。(相当于编码器的开关(当输入0时编码器工作))(当电路禁止工作时,输出为111)

4)EO非表示选通输出端,当EO非为0时表示电路在工作状态但是没有输入。(用于区分开电路禁止工作时无输入的情况(等于0的时候))

5)GS非表示扩展输出端,当GS非为0时表示电路在工作状态并且至少存在一个输入。(用于标识电路处于工作状态并且有输入的情况)

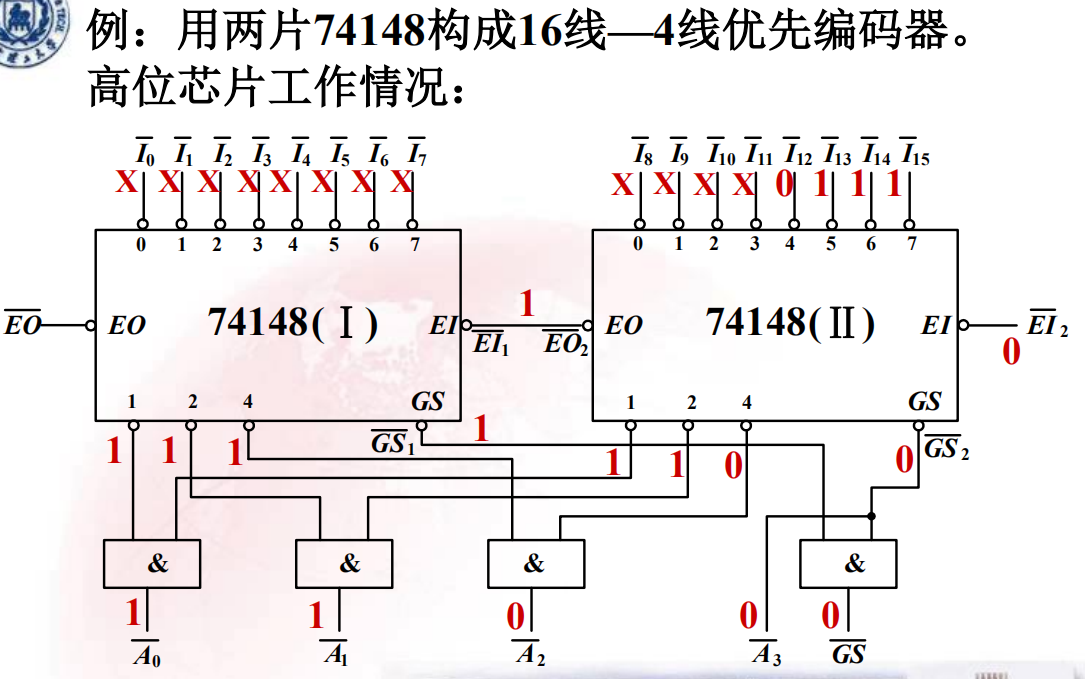

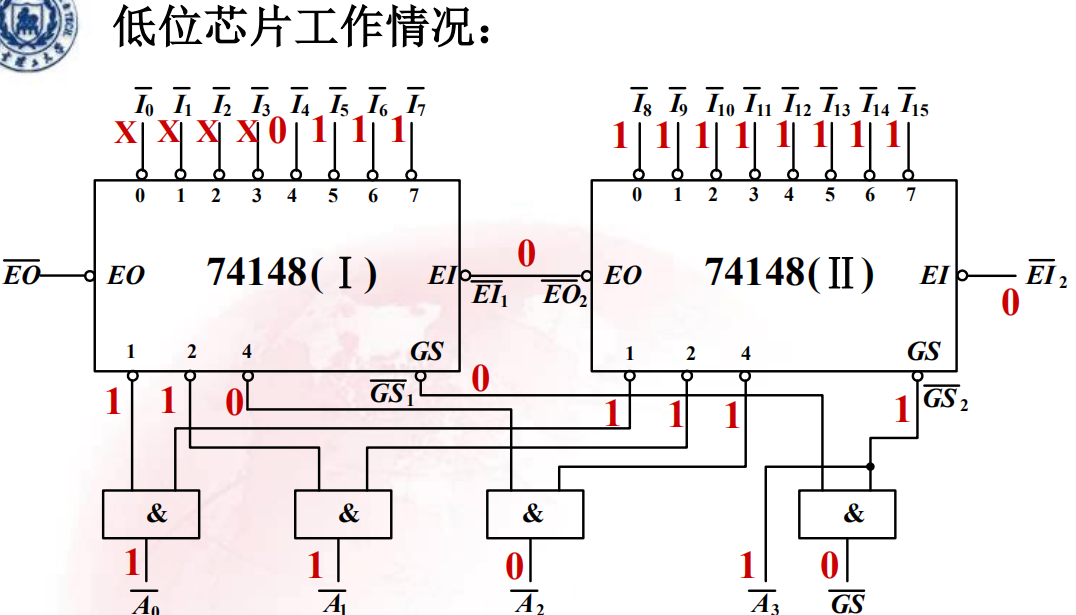

使用两块74148来构成一个16线 — 8线编码器:

当II编码器工作时,EI非输入使能端为0将II编码器打开,此时如果存在输入,则EO非为1,同时将EO非接入下一片I编码器的输入使能端。将I编码器关闭。I编码器输出全为1。

当II编码器工作时,如果有输入时,GS非的输出都为0。将GS非输出的0作为编码后的最高位,即0111中的0(低电平有效)。此时按照8线—3线编码器中将II编码器中的输入编码成为一个3位的二进制编码,和I编码器的111相与之后的结果加上最高位的0即为最终的编码。

当I编码器工作时,II编码器的EI非端输入还为0,但是此时的II编码器的输入全为1,即无输入。此时II编码器的EO非输出为0,表示II编码器正在工作但是没有输入。此时输出的EO非输入到I编码器中的EI非中,将I编码器开启进行编码,此时的II编码器的所有输出都为111(低电平有效)。并且II编码器的GS非端的输出为1,即最高位此时为1(低电平有效)。I编码器将输入编码为一个三位二进制数后和II编码器中的111相与,即为最后编码的结果。

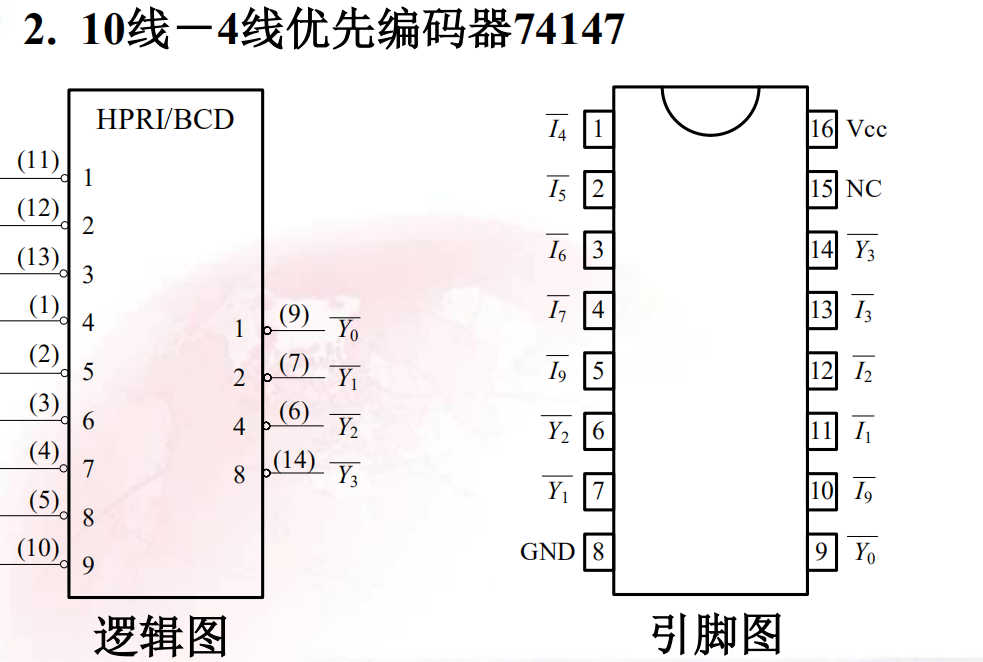

10线—4线优先编码器74147

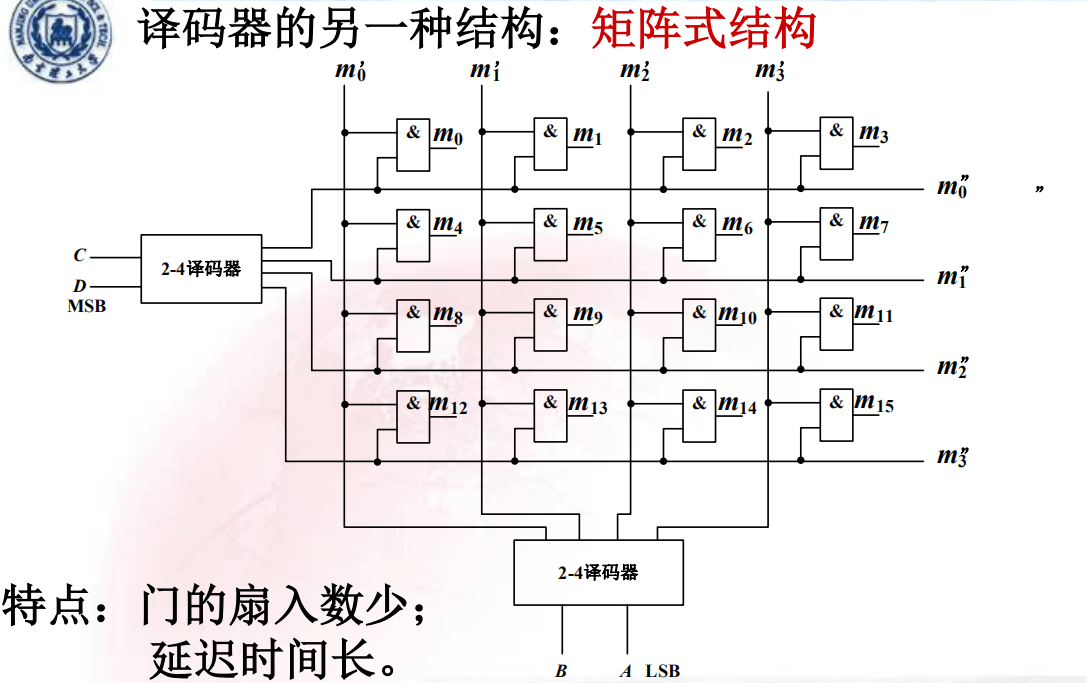

译码器/数据分配器

译码是编码的逆过程,作用是将一组码转换为确定信息。

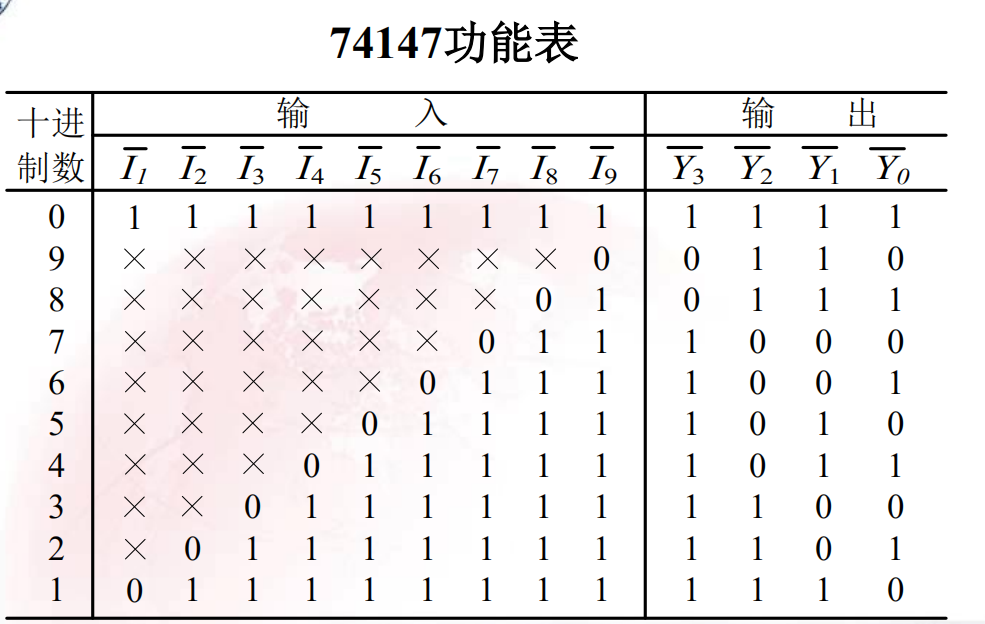

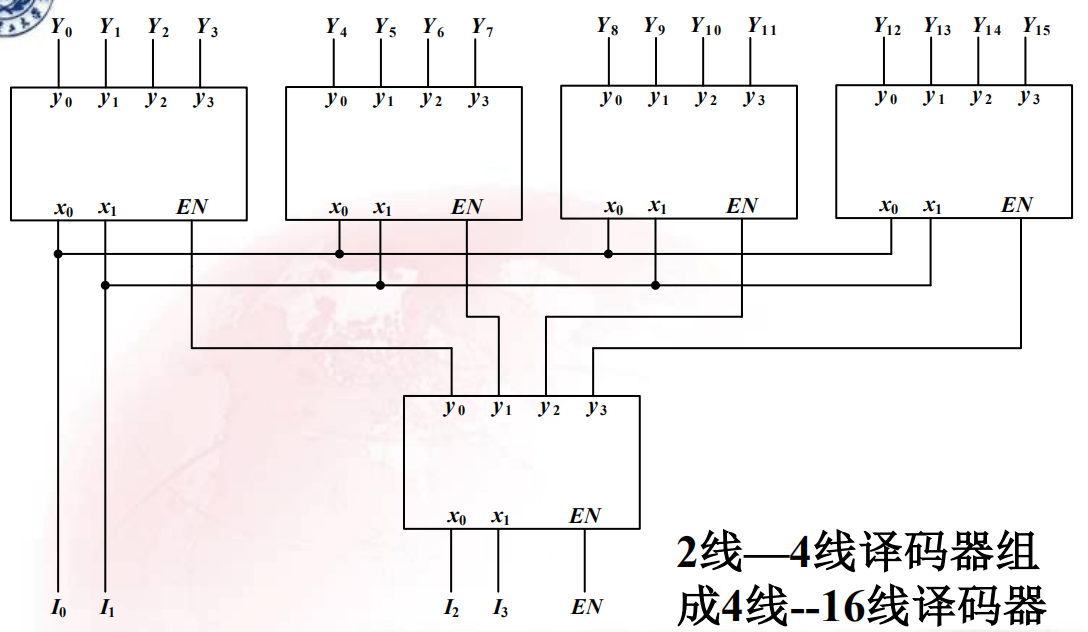

二进制译码器

输入:二进制代码,有n个;

输出:2n 个特定信息。

LSB:最低有效位

MSB:最高有效位

高电平输出有效的二进制译码器的输出逻辑表达式为Yi = mi(mi为输入变量所对应的最小项)

低电平输出有效的二进制译码器的输出逻辑表达式为Yi非 = mi非(mi为输入变量所对应的最小项)

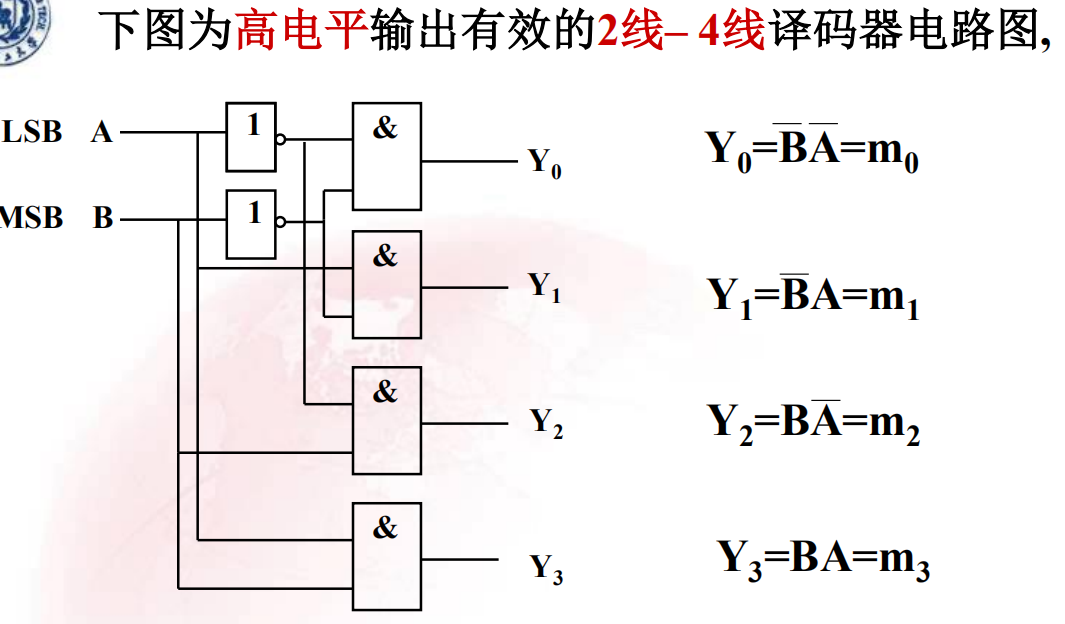

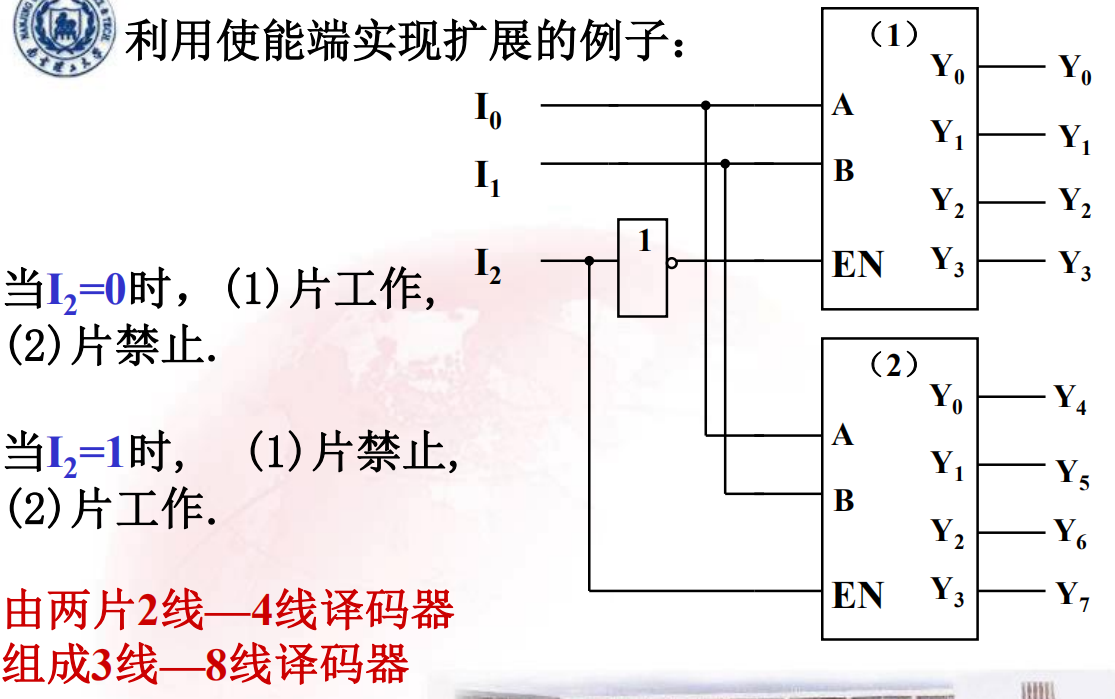

译码器的使能控制端

1)利用使能输入控制端,既能使电路正常工作,也能使电路处于禁止工作状态;

2)利用使能输入控制端,能实现译码器容量扩展。

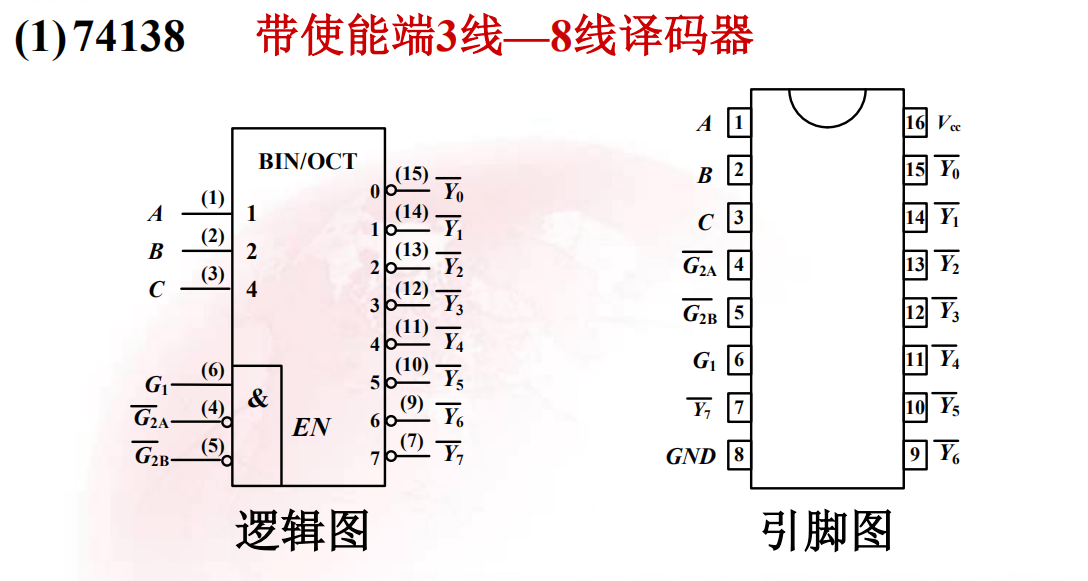

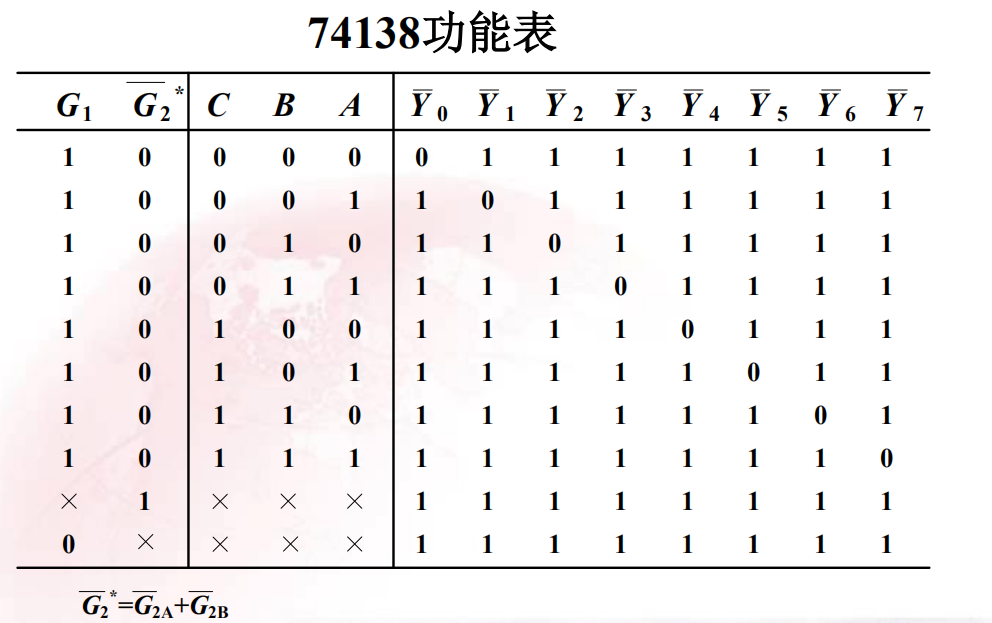

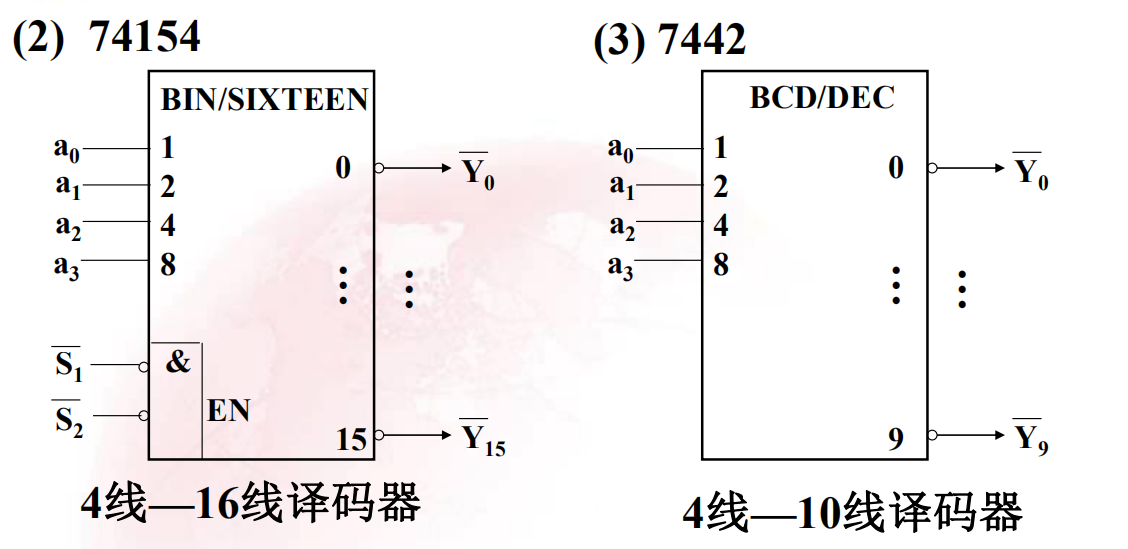

通用译码器集成电路

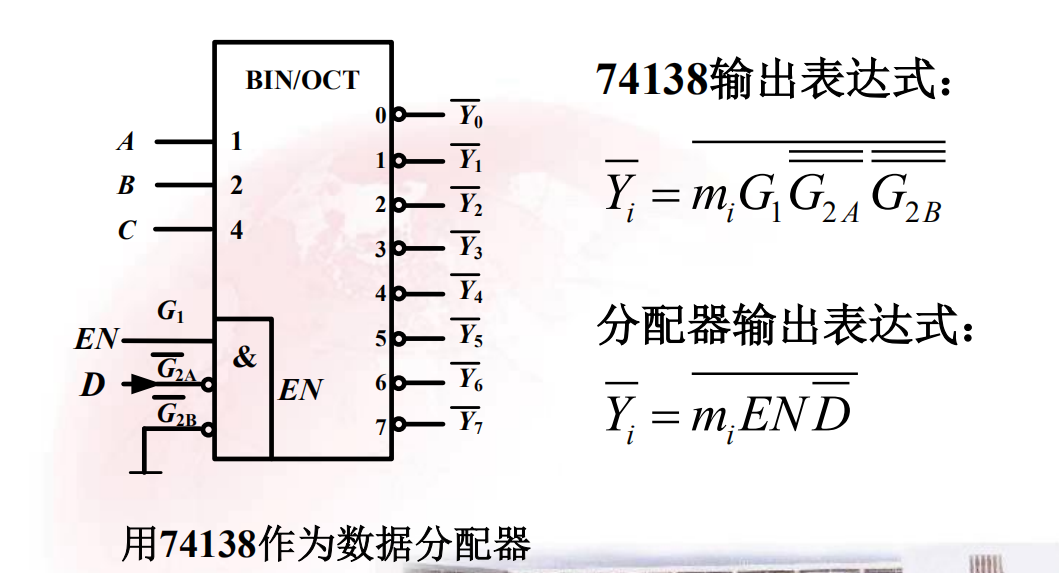

带使能端3线—8线译码器 74138

1)电路输出低电平有效

2)G1,G2A,G2B的值分别为100,此时电路才进行工作,否则,电路禁止工作。电路输出均为1。

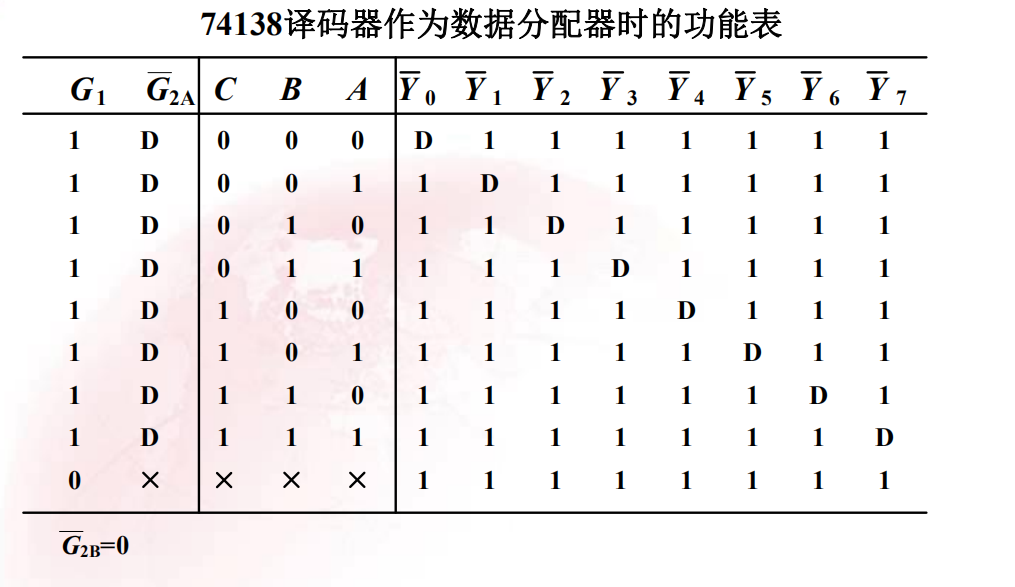

数据分配器

数据分配是将一个数据源输入的数据根据需要送到不同的输出端上去,实现数据分配功能的逻辑电路称为数据分配器。分配器又叫多路复用器。

数据分配器一般用带使能控制端的二进制译码器实现。

用74138作为数据分配器

此时D即为数据源,通过CBA的编码来将D的数据分配到0~7的某一个出口处。

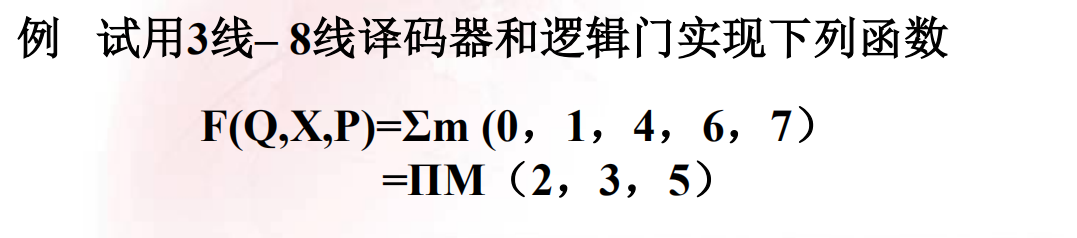

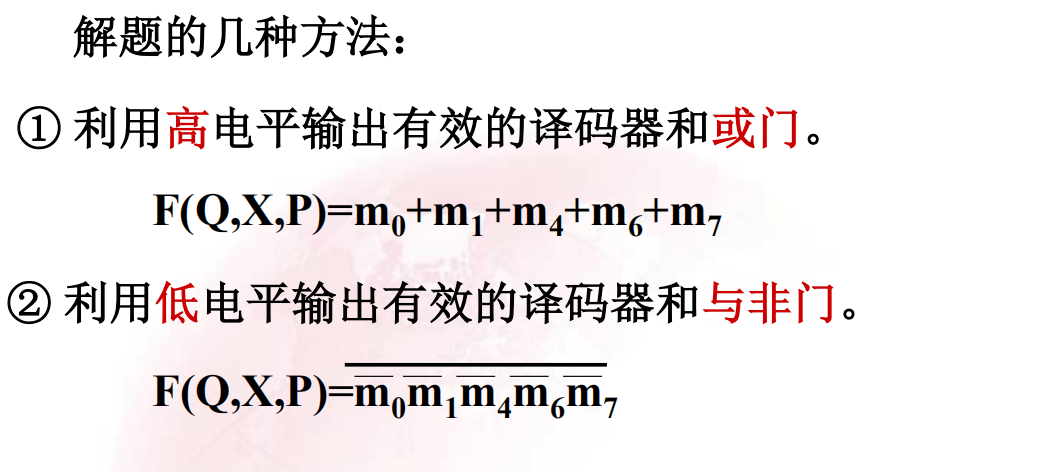

译码器应用举例

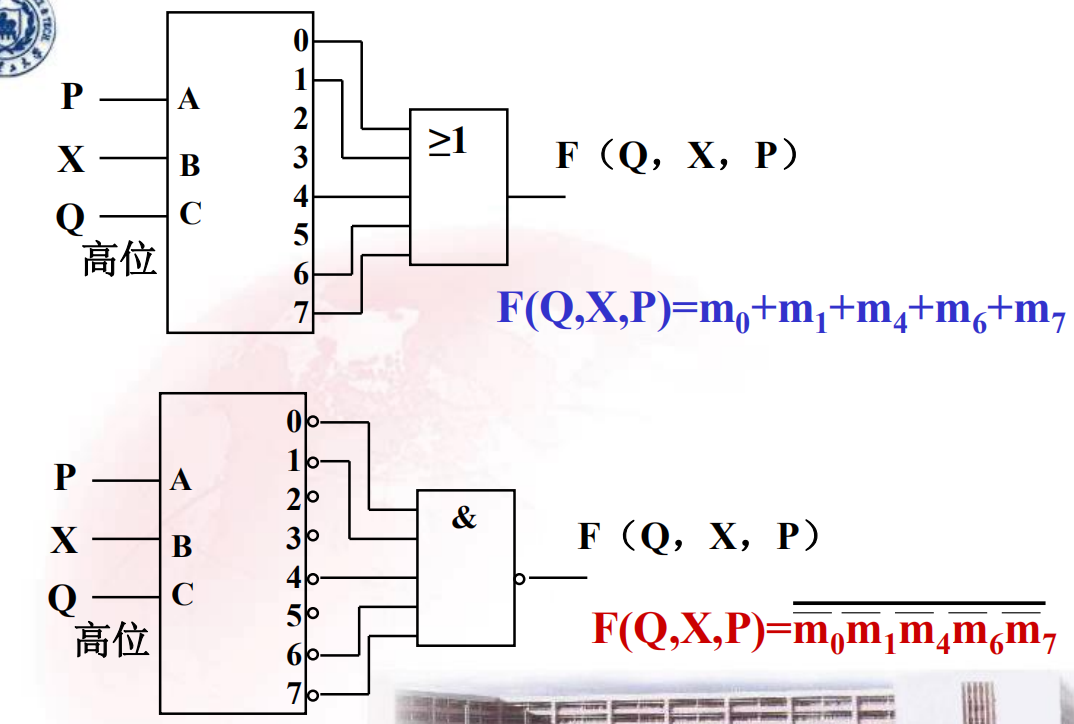

用译码器实现组合逻辑函数

原理: 二进制译码器能产生输入信号的全部最小项,而所有组合逻辑函数均可写成最小项之和的形式

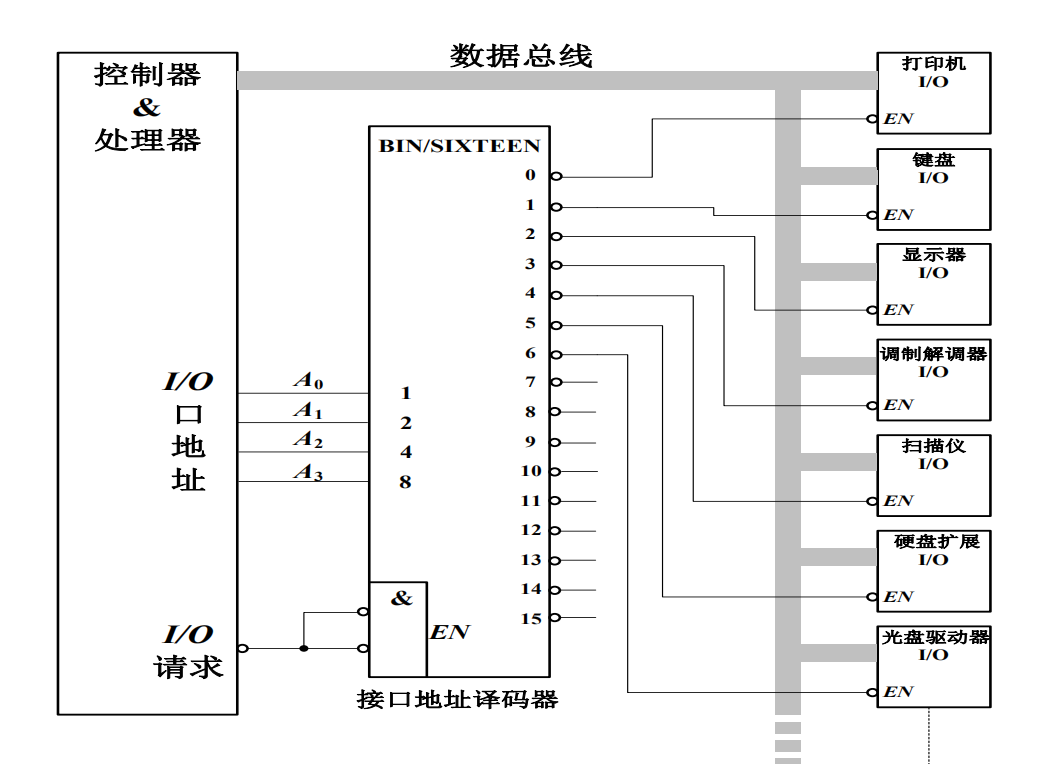

计算机输入/输出接口地址译码电路

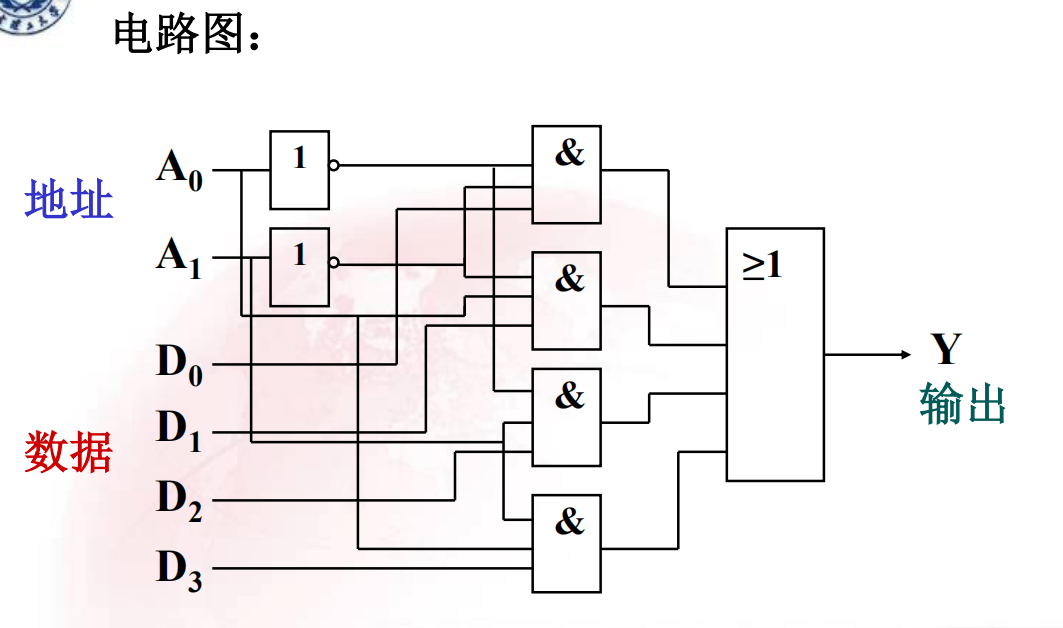

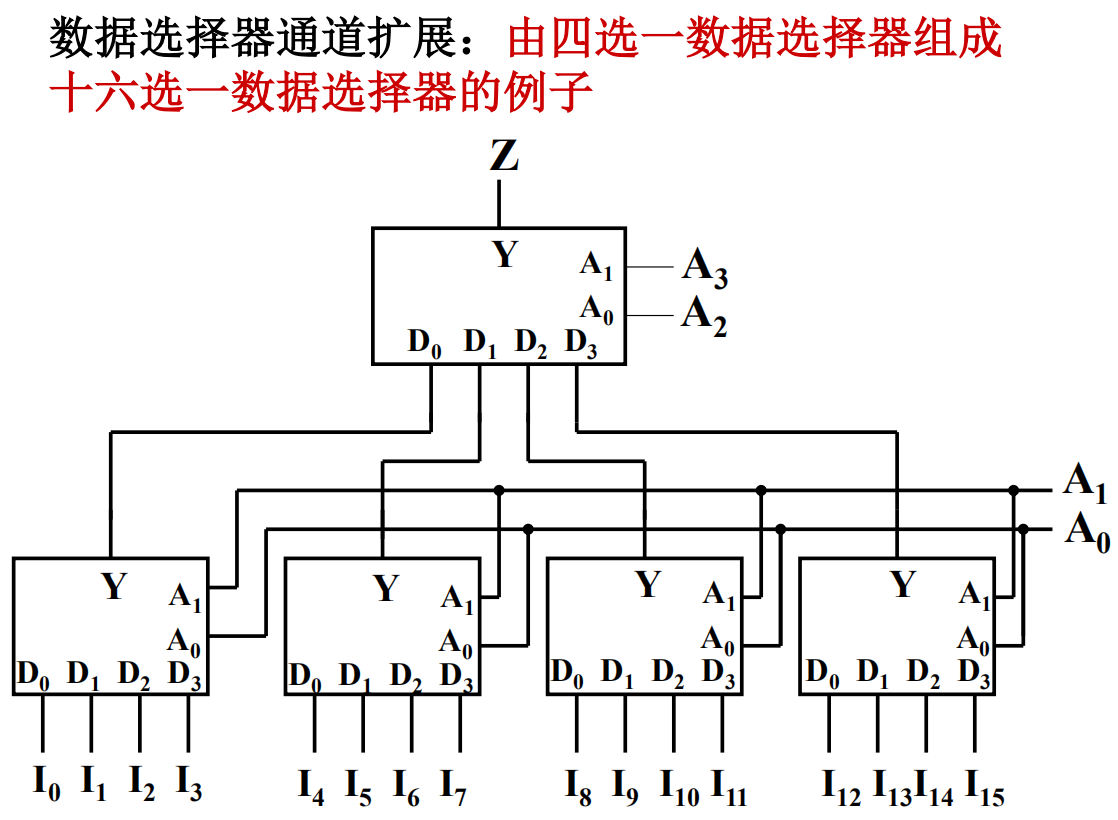

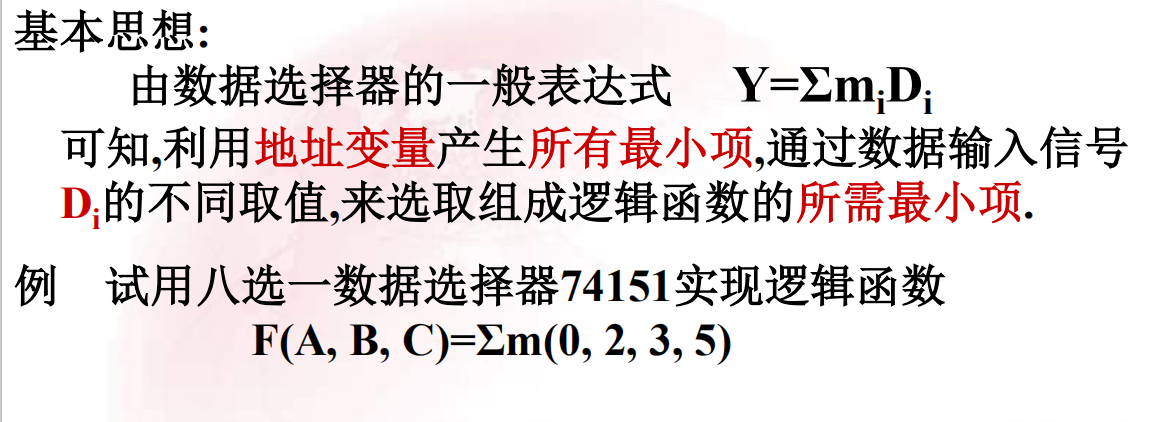

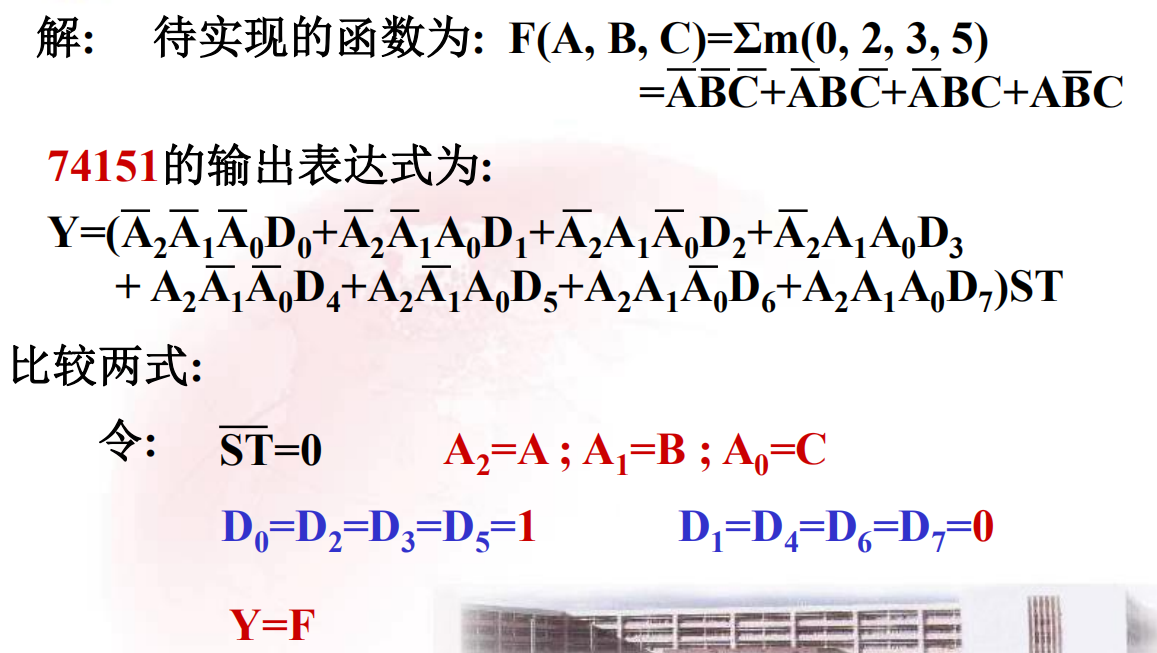

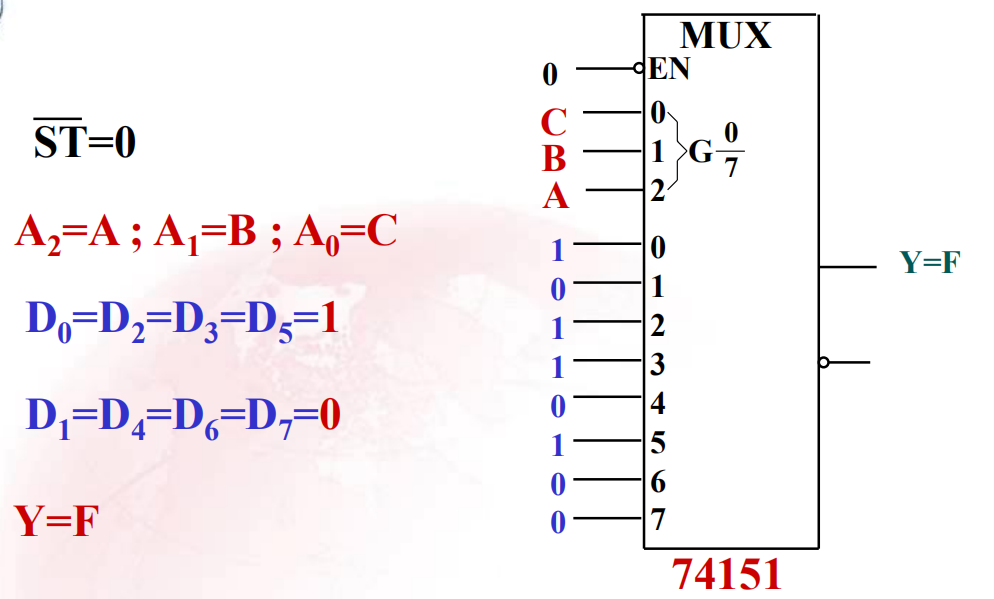

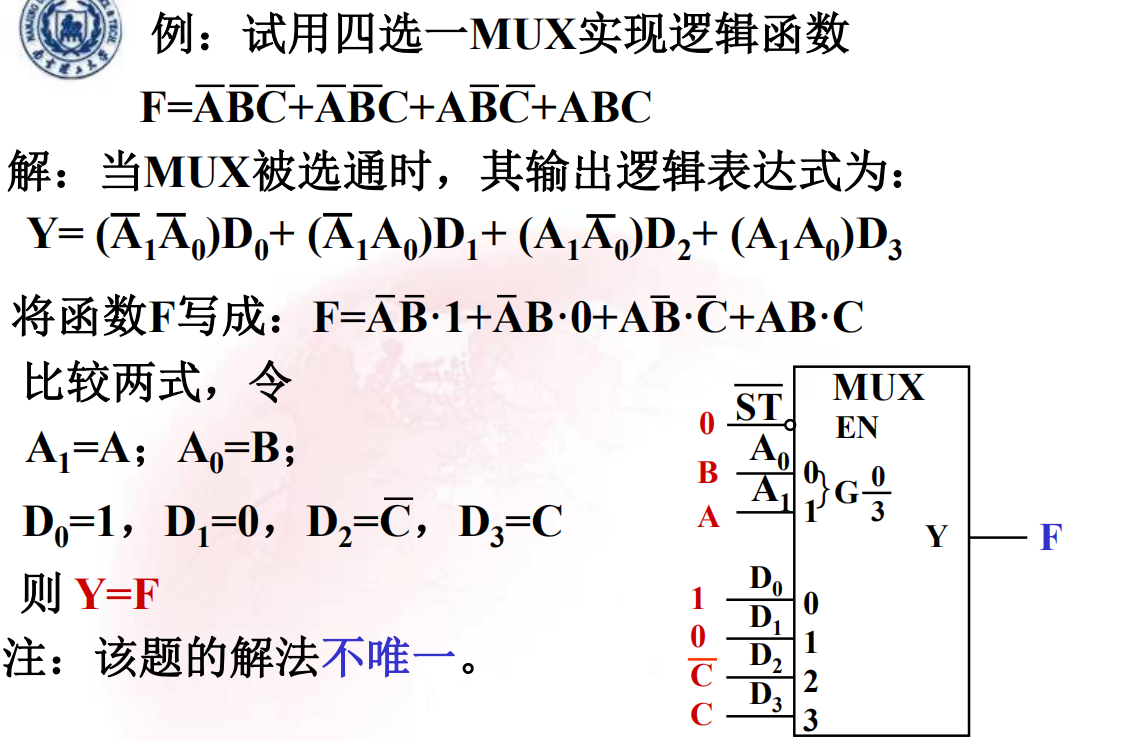

数据选择器

功能: 从多路输入数据中选择其中的一路送至输出端.

数据选择器简称MUX,数据选择器的数据输入端数称为通道数

常用MUX数据选择器的编号有:74150(16个输入),74151(8个输入)

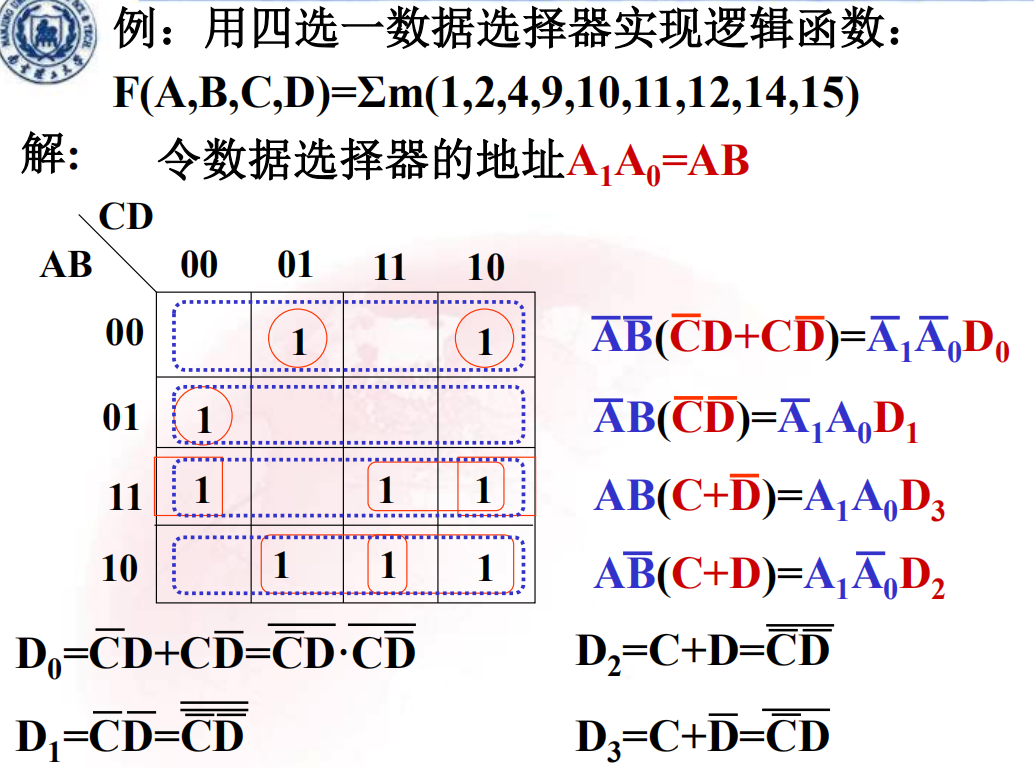

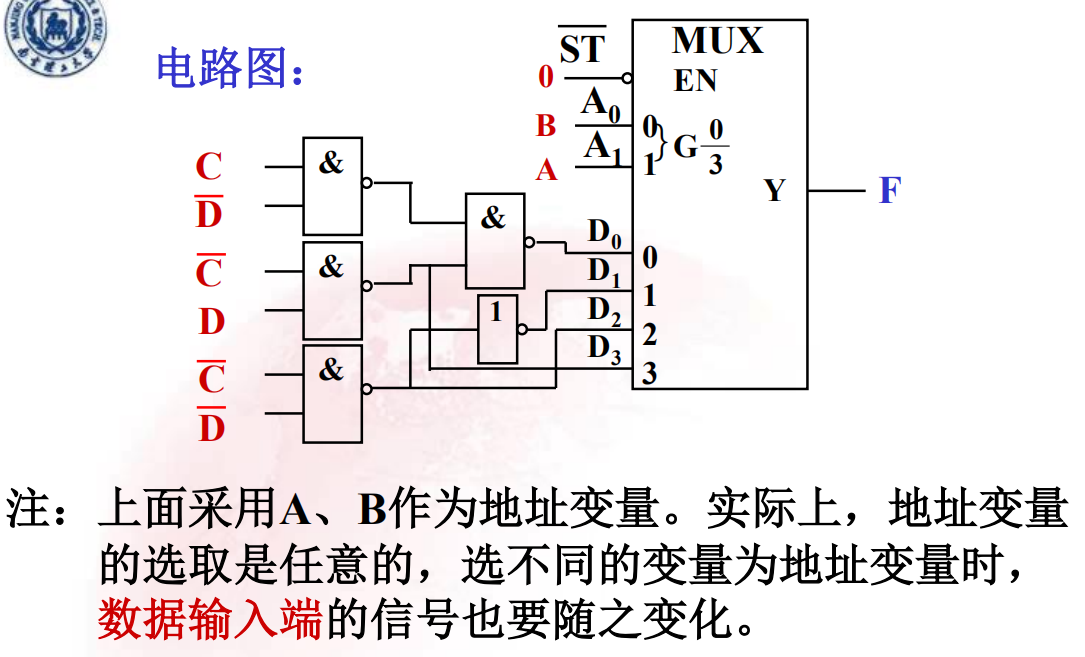

数据选择器应用实例

1)用MUX实现逻辑函数时,MUX必须被选通,即ST非=0

2)变量和地址端之间的连接必须正确。

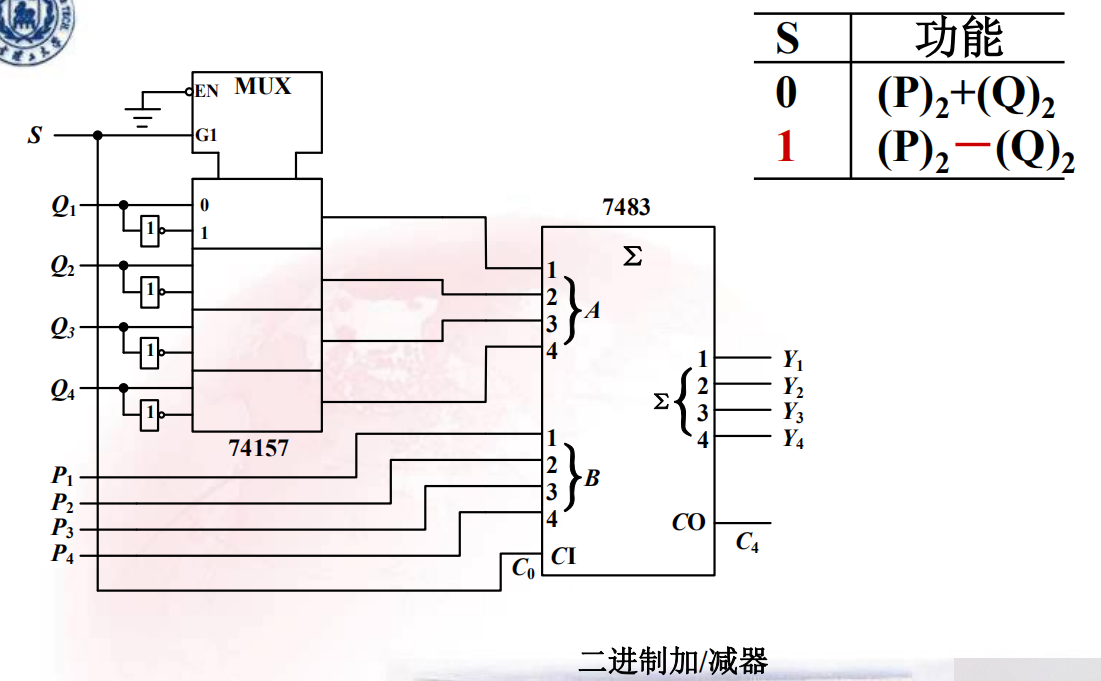

算数运算电路

算术运算电路的核心为加法器.

基本加法器

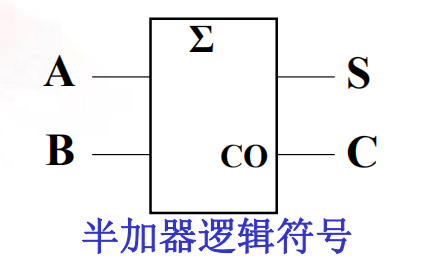

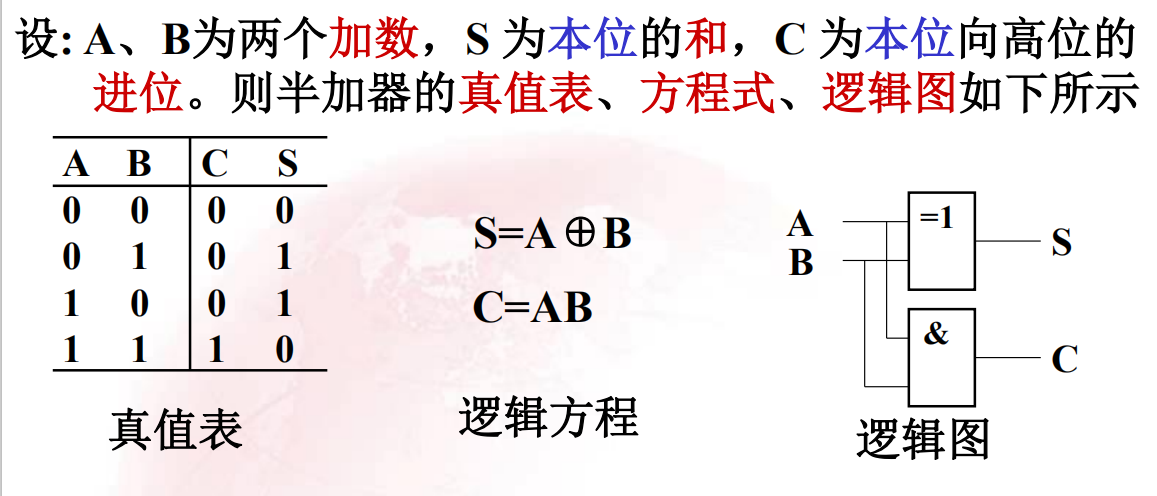

1)半加器(HA):

仅考虑两个一位二进制数相加,而不考虑低位的进位,称为半加。

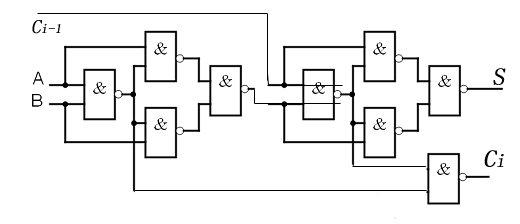

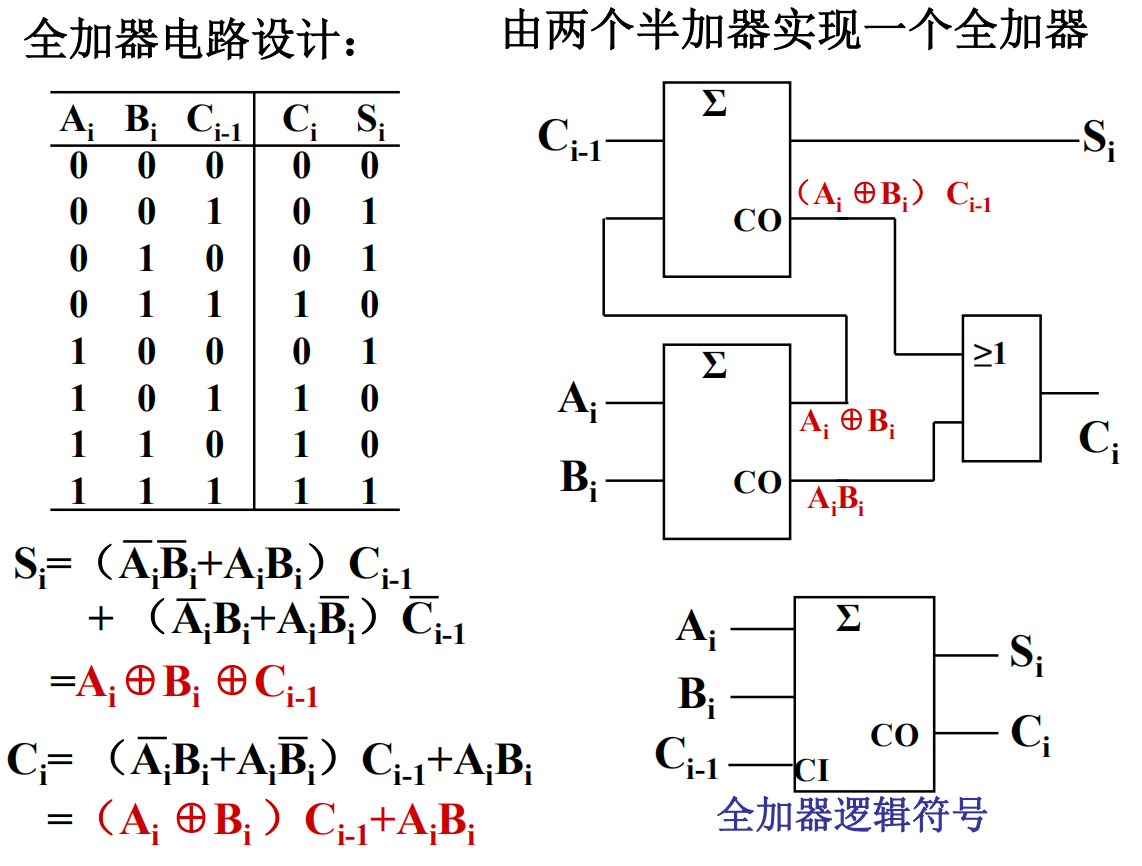

2)全加器:在多位数相加时,除考虑本位的两个加数外,还须考虑低 位向本位的进位 image-20211225160552401

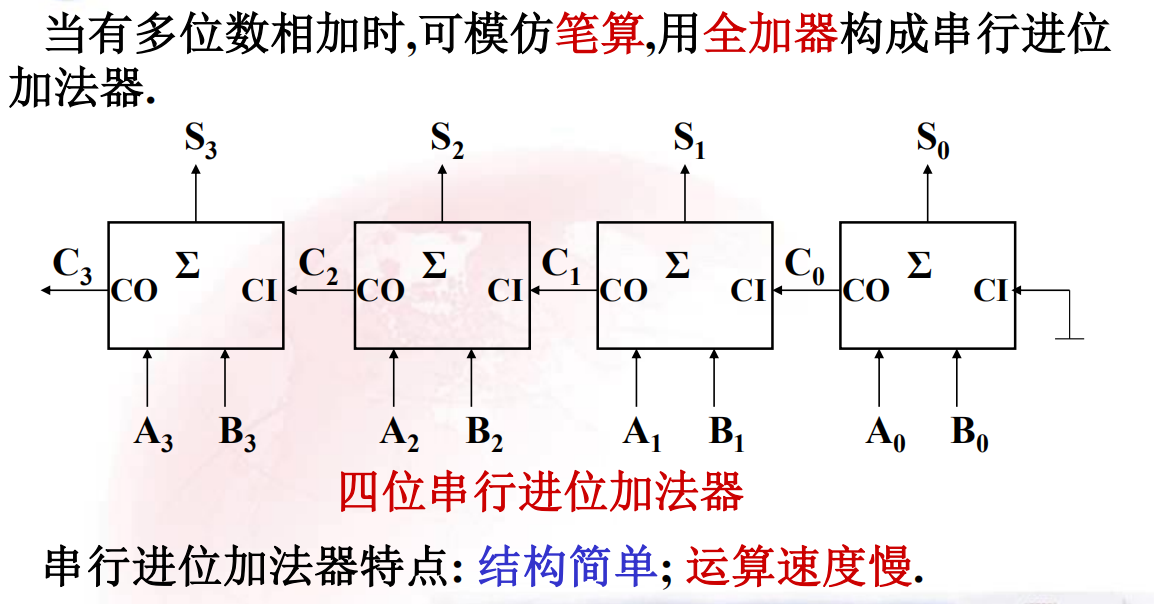

3) 串行进位加法器:

高速加法器

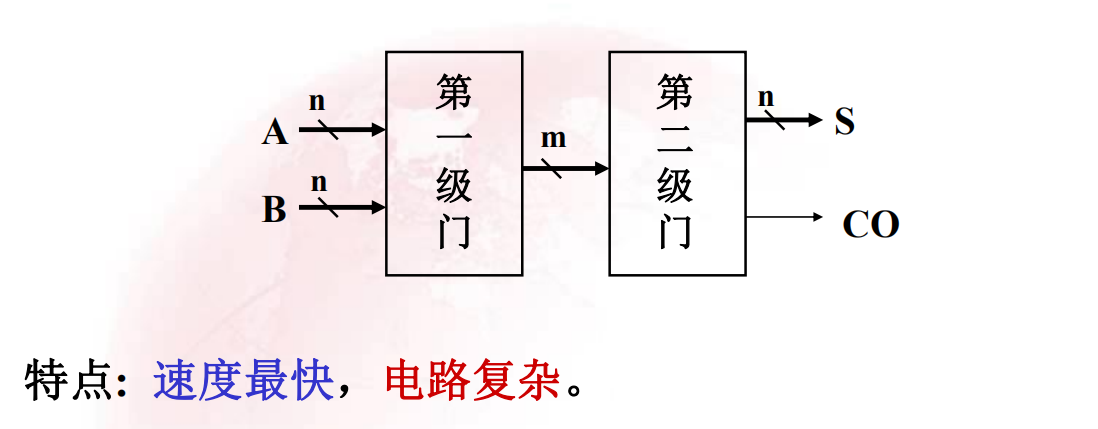

1)全并行加法器

只存在在理论中。

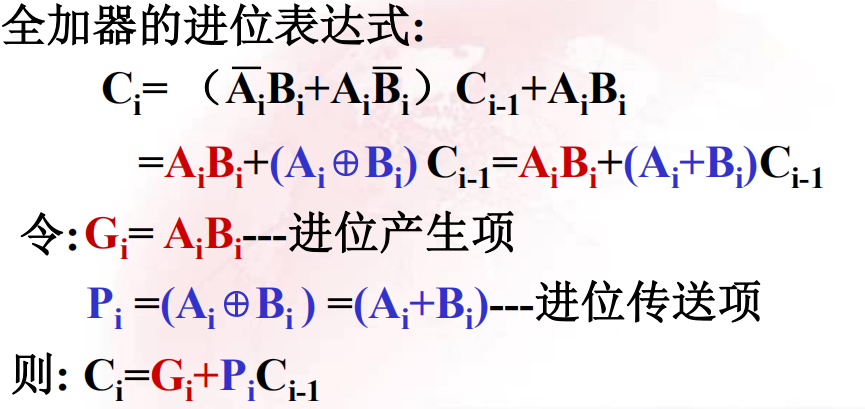

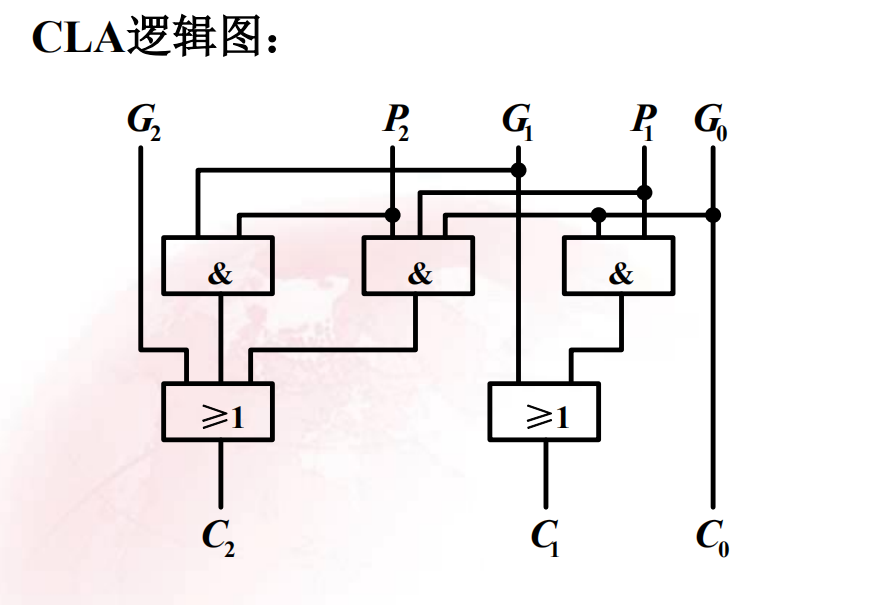

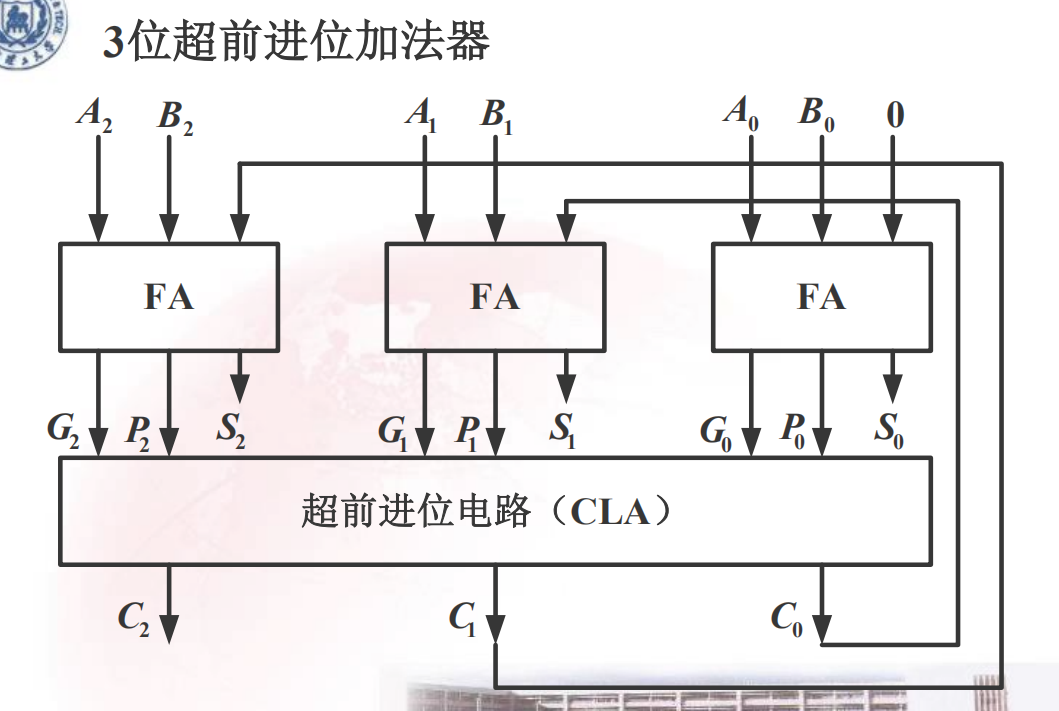

2)超前进位加法器

设计思想: 由两个加数,首先求得各位的进位,然后再经全加器算出结果

根据Gi 、Pi 来求进位信号C 的电路称为超前进位电路(CLA)

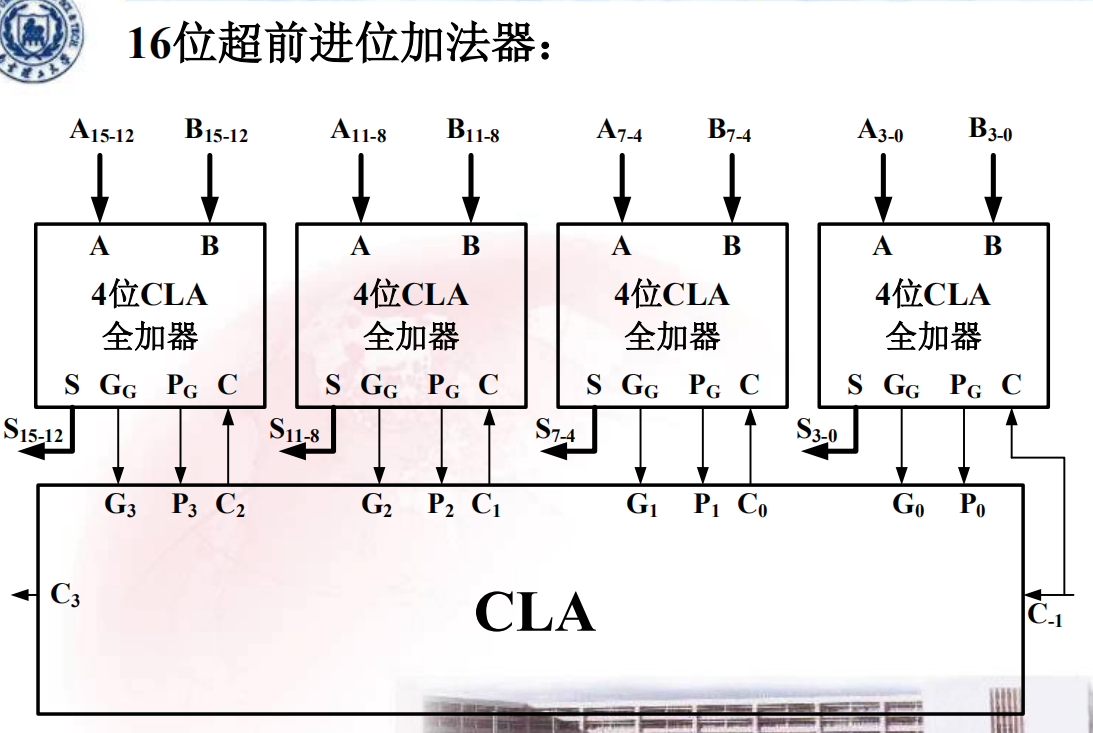

超前进位加法器的缺点在于超前进位逻辑的产生,随着位数的增加,Ci会变得很复杂。

超前进位加法器的实现通常以4位为基本模块,以分层结构实现位数为4 的倍数的加法器。由C3完整表达式:

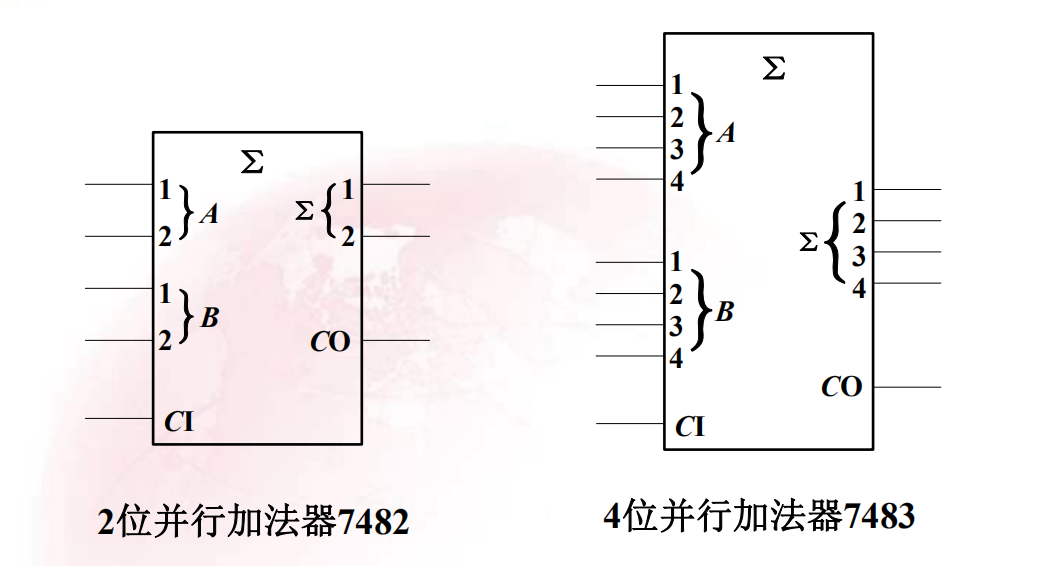

通用加法器集成电路

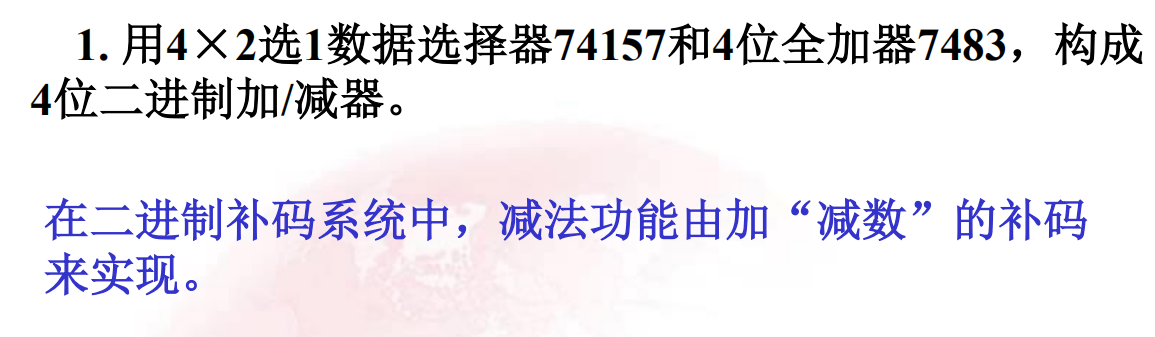

例题:

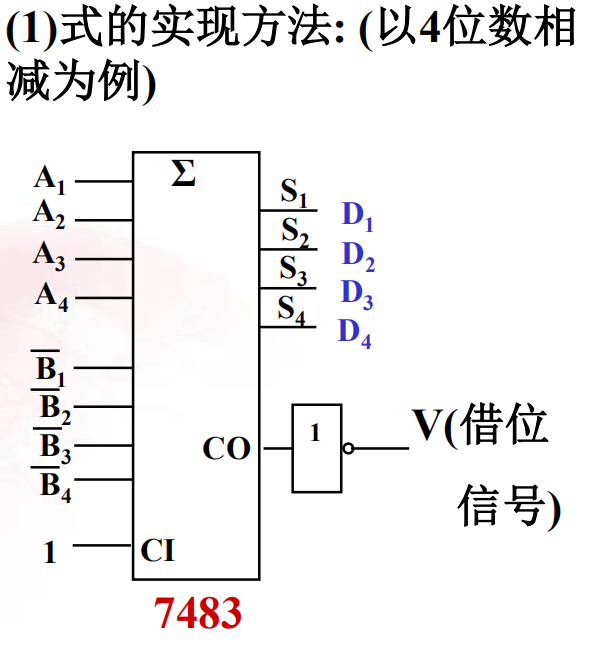

减法电路

借位信号实现减2的n次方 的功能: 当A+B反+1 的高位有进位时,

该进位信号和2的n次方 相减使最高位为0, 反之为1。

借位信号作为运算结果的符号位。

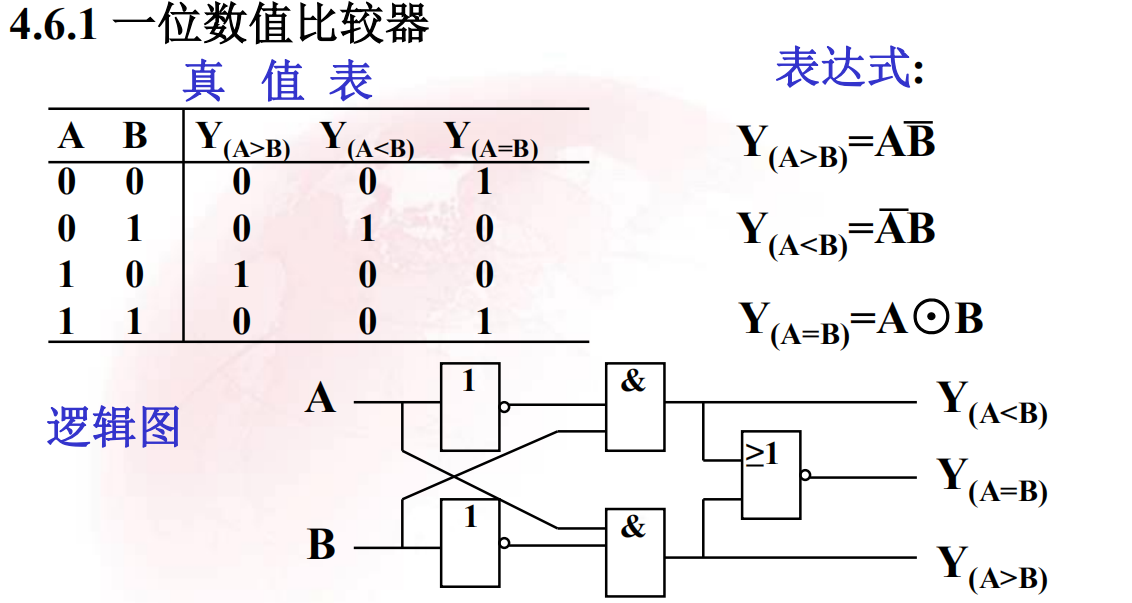

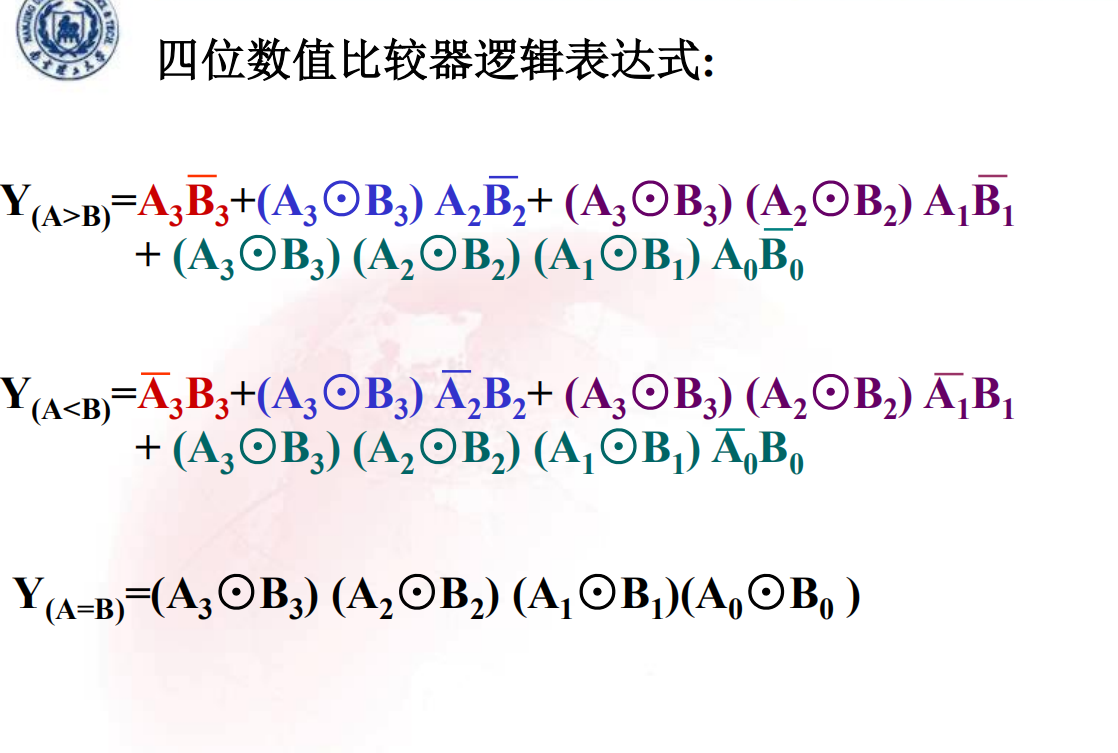

数值比较器

数值比较器用来判断两个二进制数的大小或相等

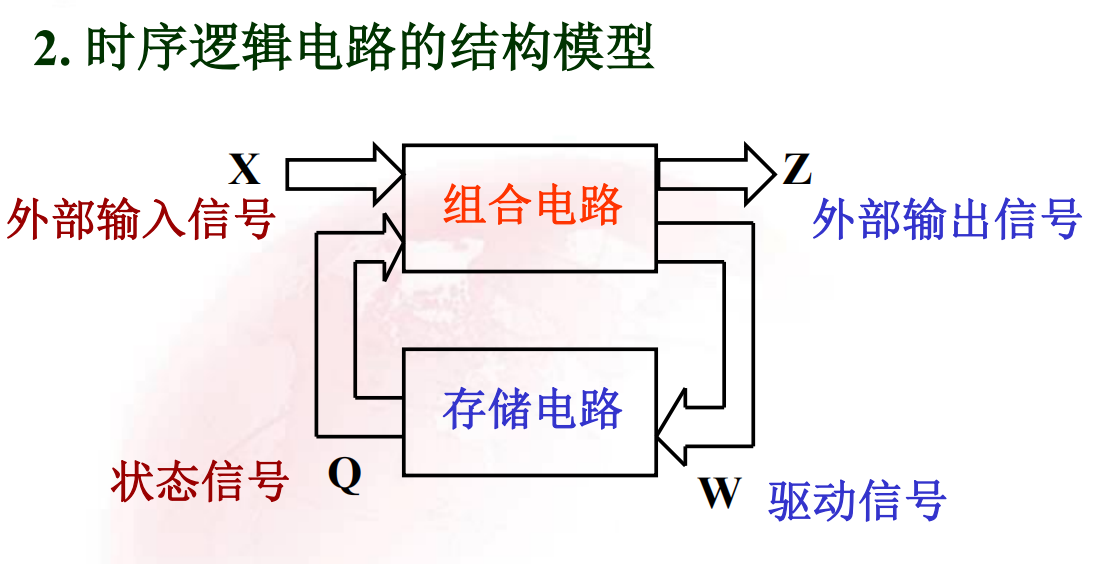

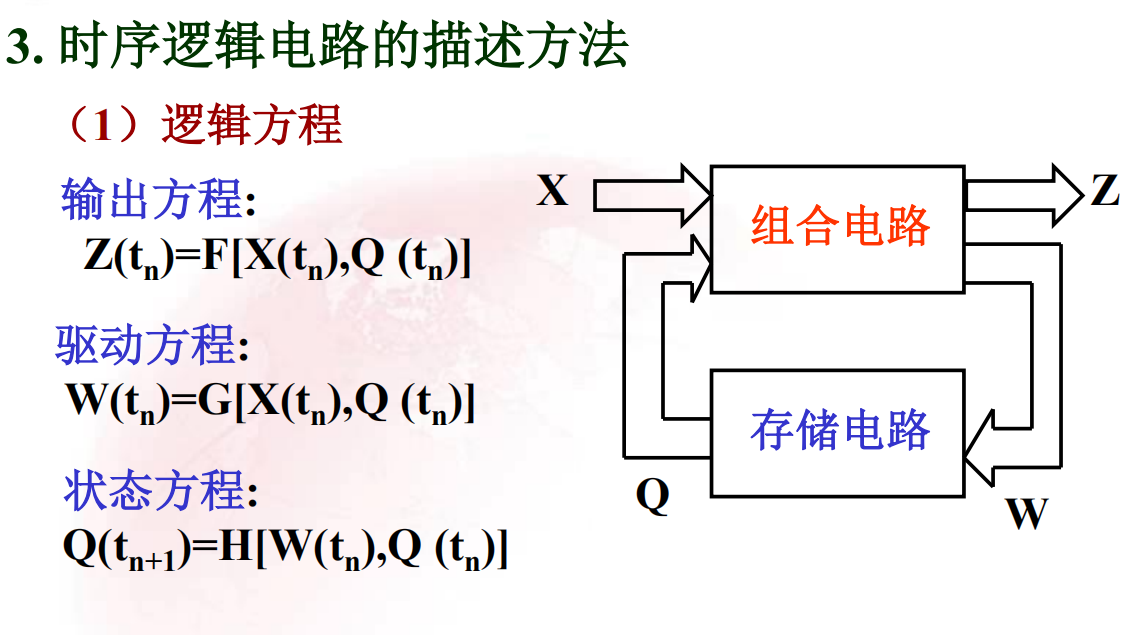

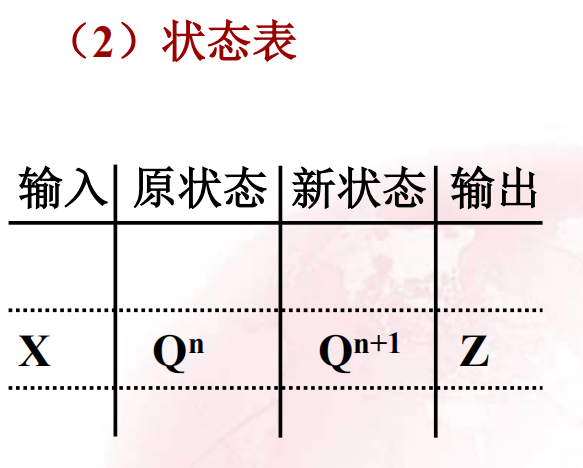

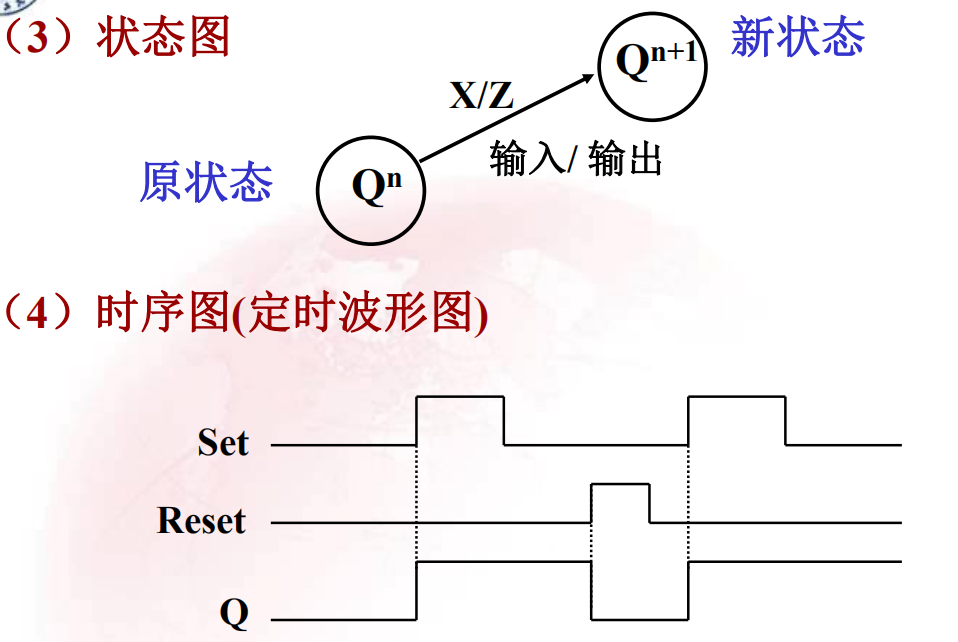

第五章 时序逻辑电路

- 时序逻辑电路的特点:

电路在任何时候的输出稳定值,不仅与该时刻的输入信号有关,而且与该时刻以前的电路状态有关;电路结构具有反馈回路。

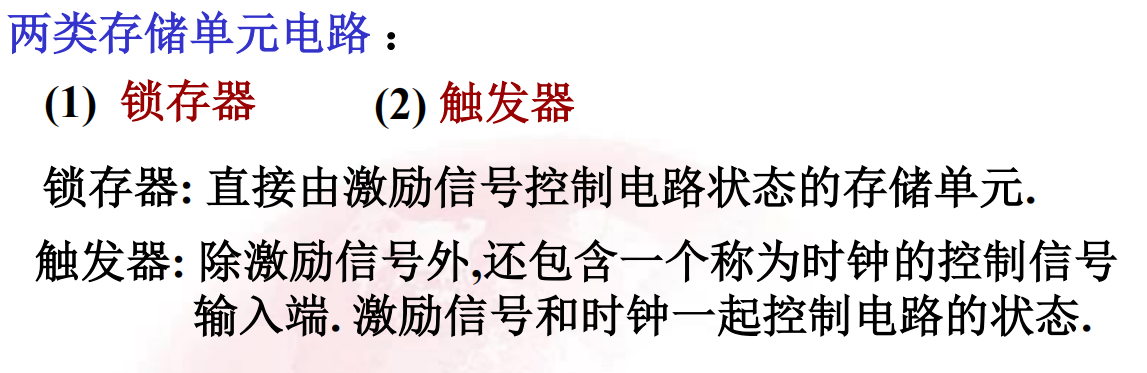

锁存器

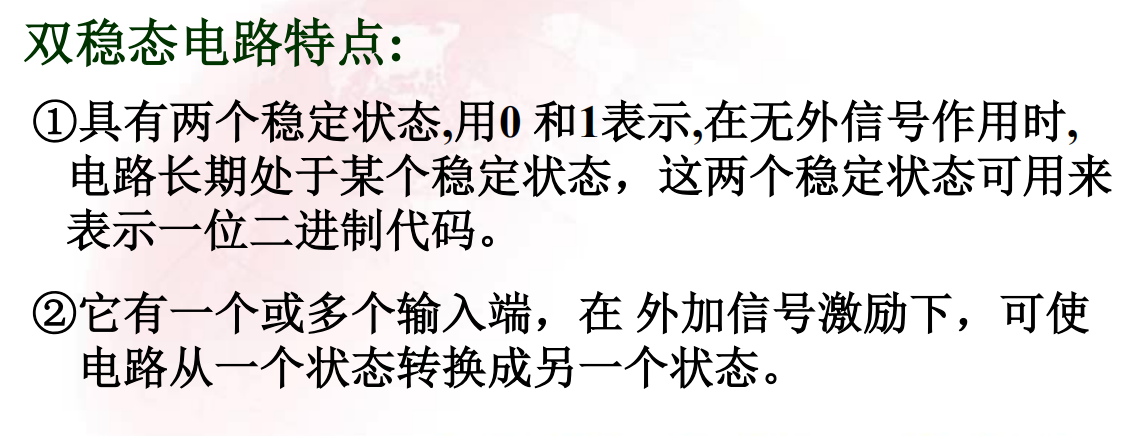

存储电路由存储器件组成,能存储一位二值信号的器件称为存储单元电路.存储单元电路大多是双稳态电路

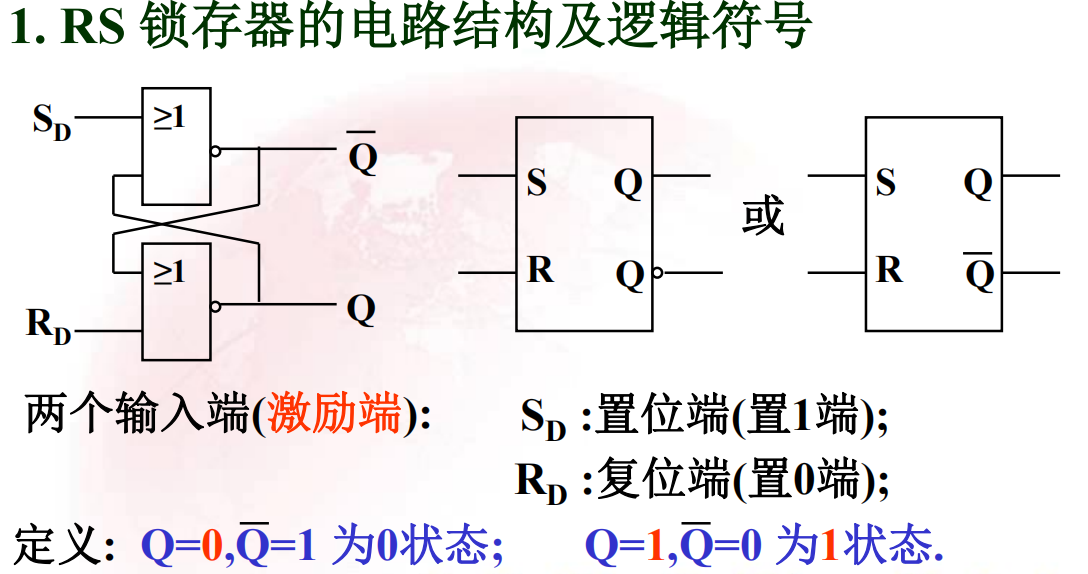

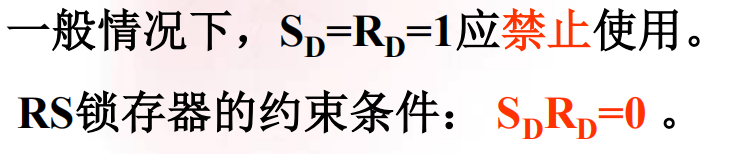

普通锁存器

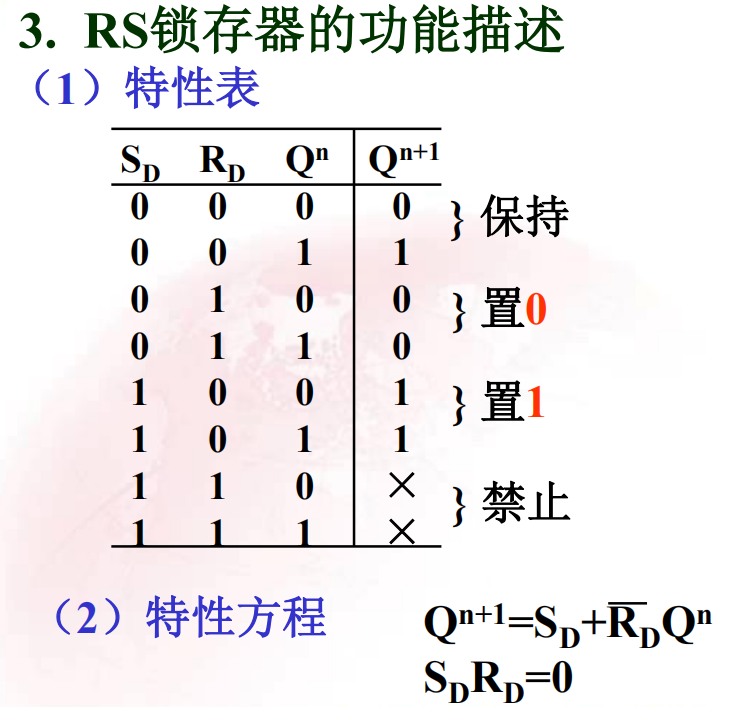

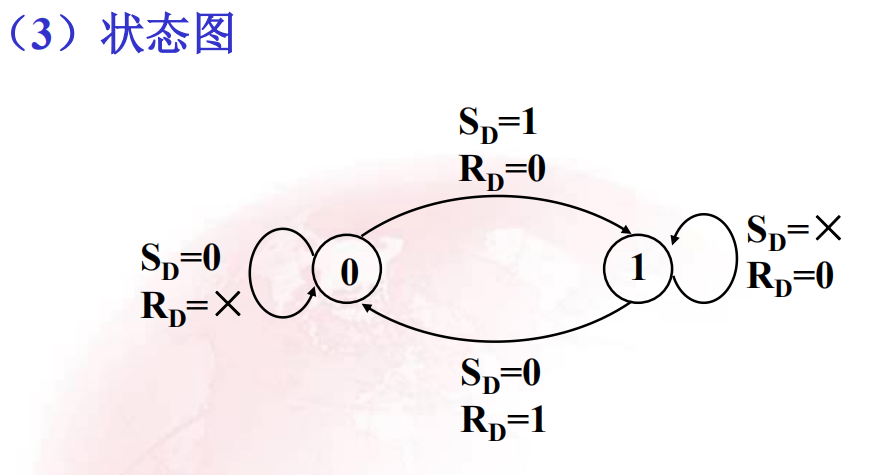

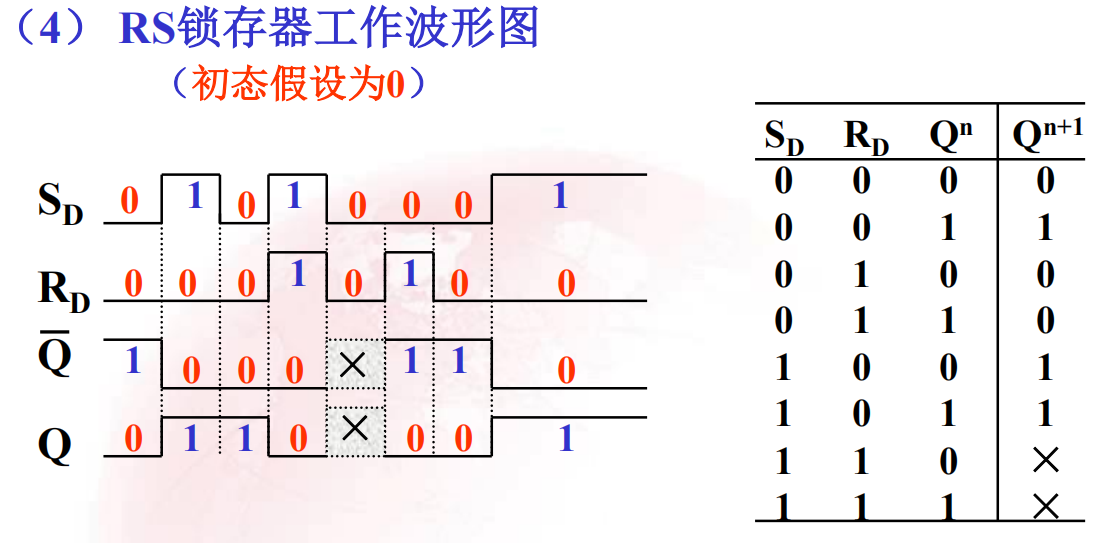

RS锁存器

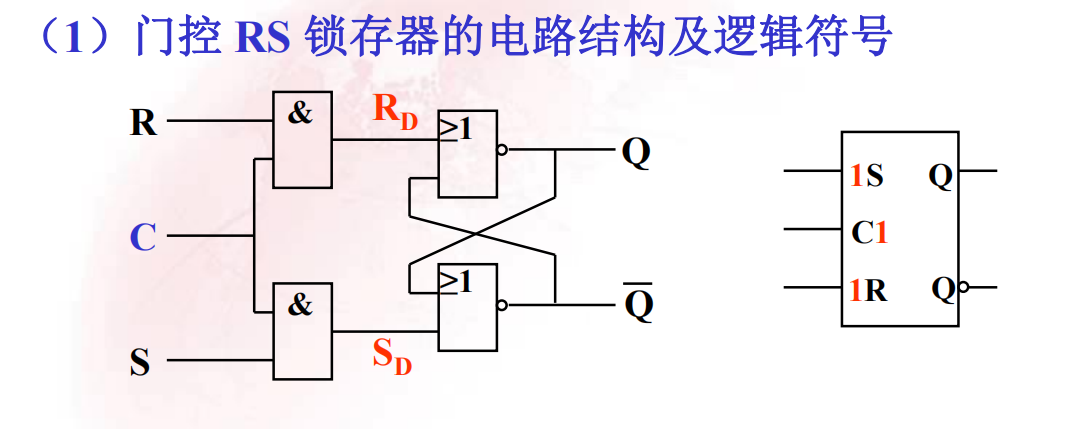

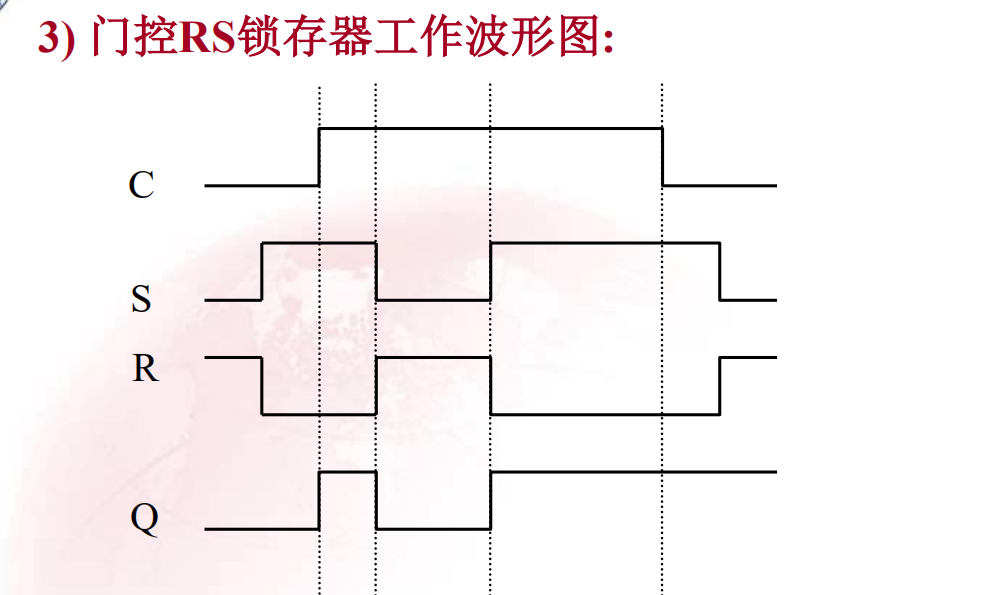

门控RS锁存器

在RS锁存器的基础上, 加控制信号,使锁存器状态转换的时间,受控制信号的控制.

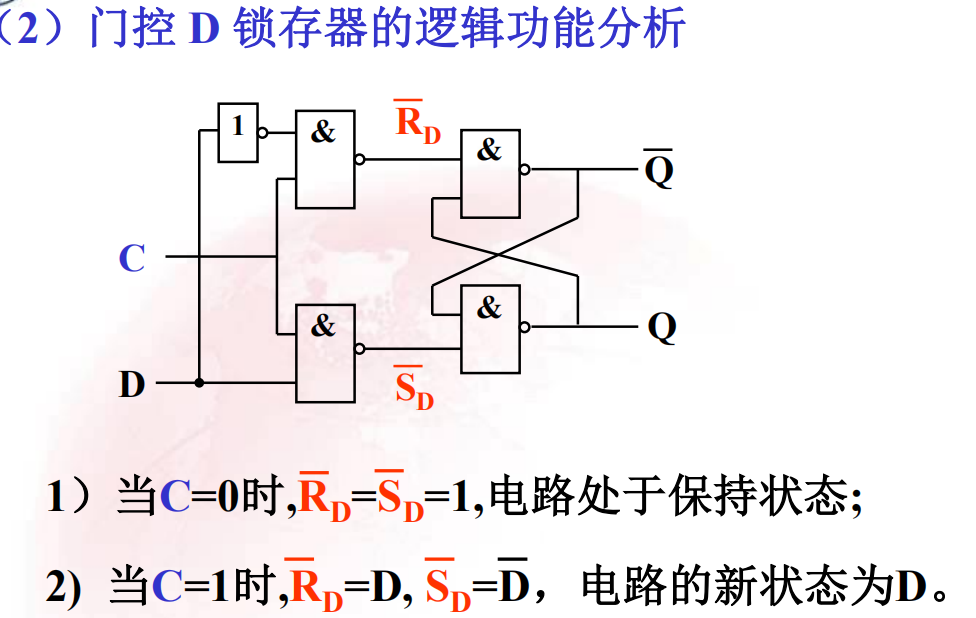

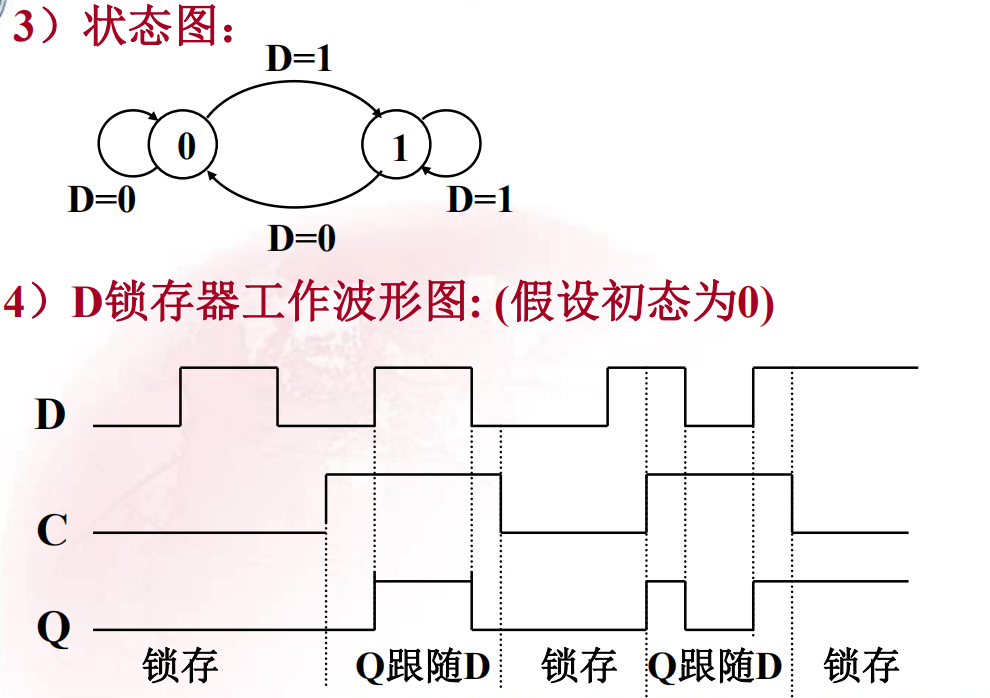

门控D锁存器

能将呈现在激励输入端的单路数据D存入交叉耦合结构的锁存器单元中.

触发器

利用一个称为“时钟”的特殊定时控制信号去限制存储单元状态的改变时间,具有这种特点的存储单元电路称为触发器。

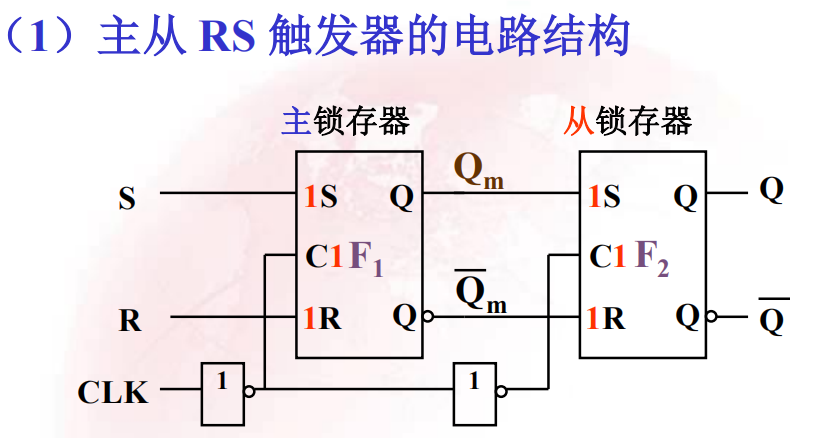

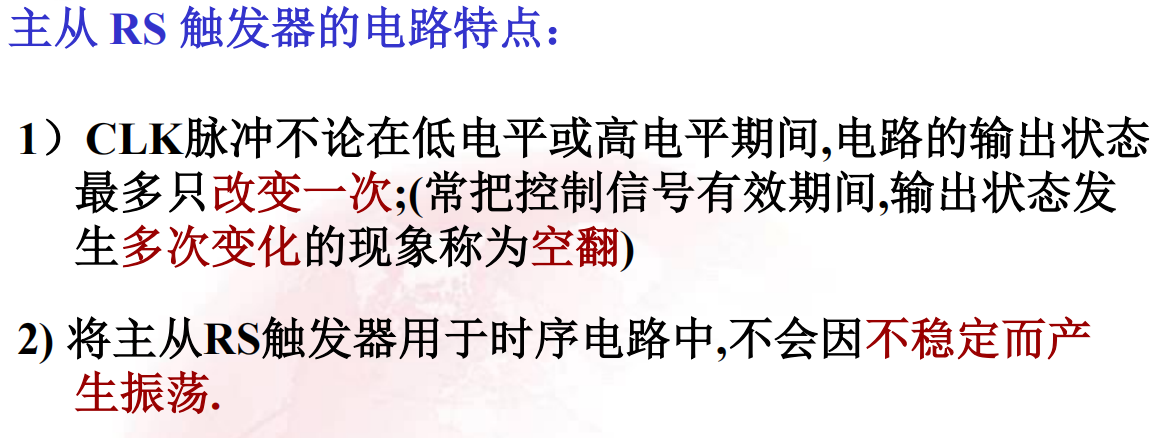

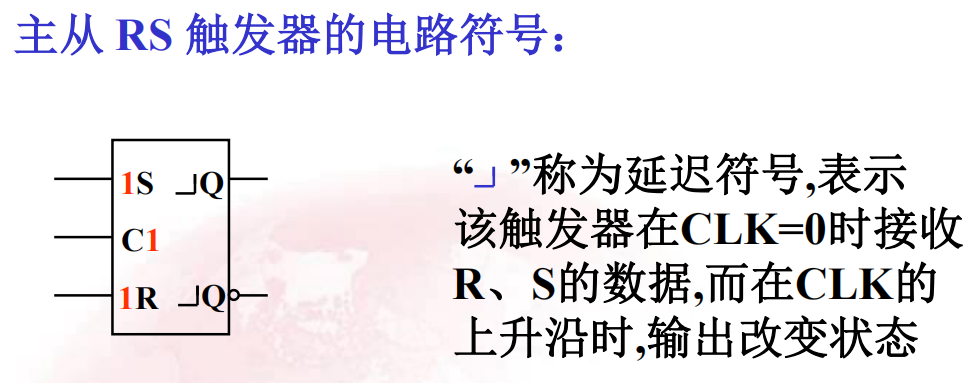

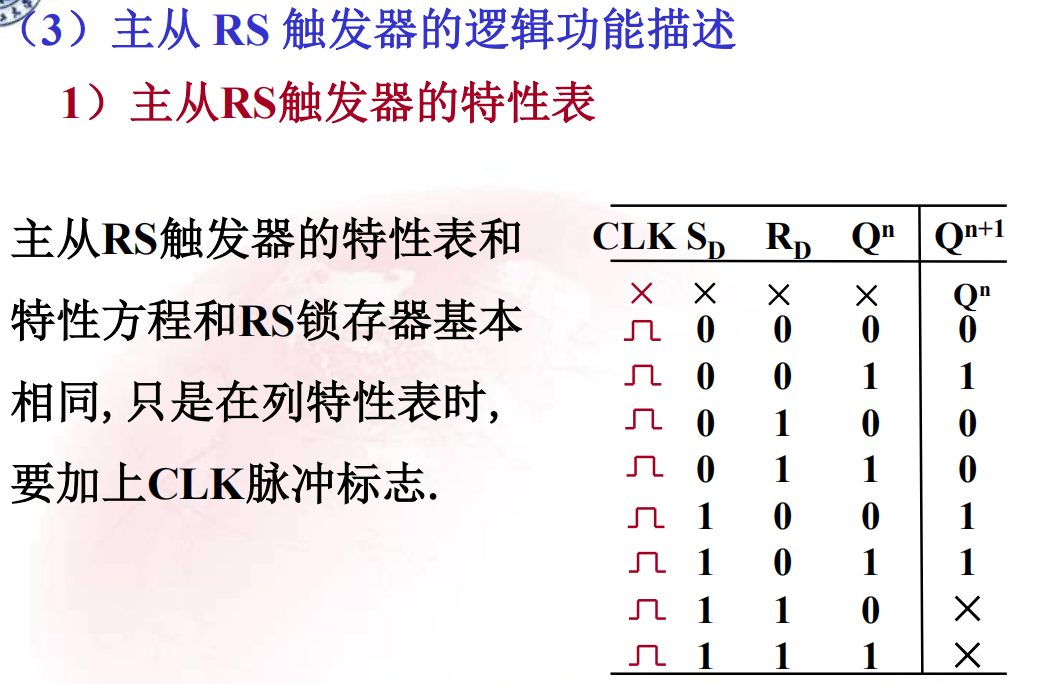

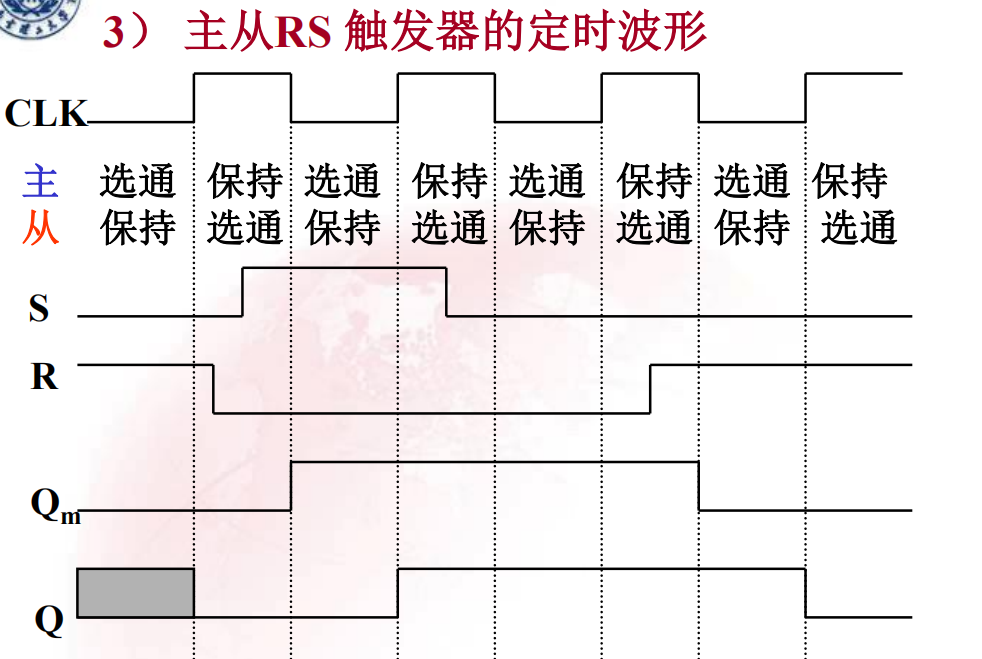

主从触发器

主从RS触发器

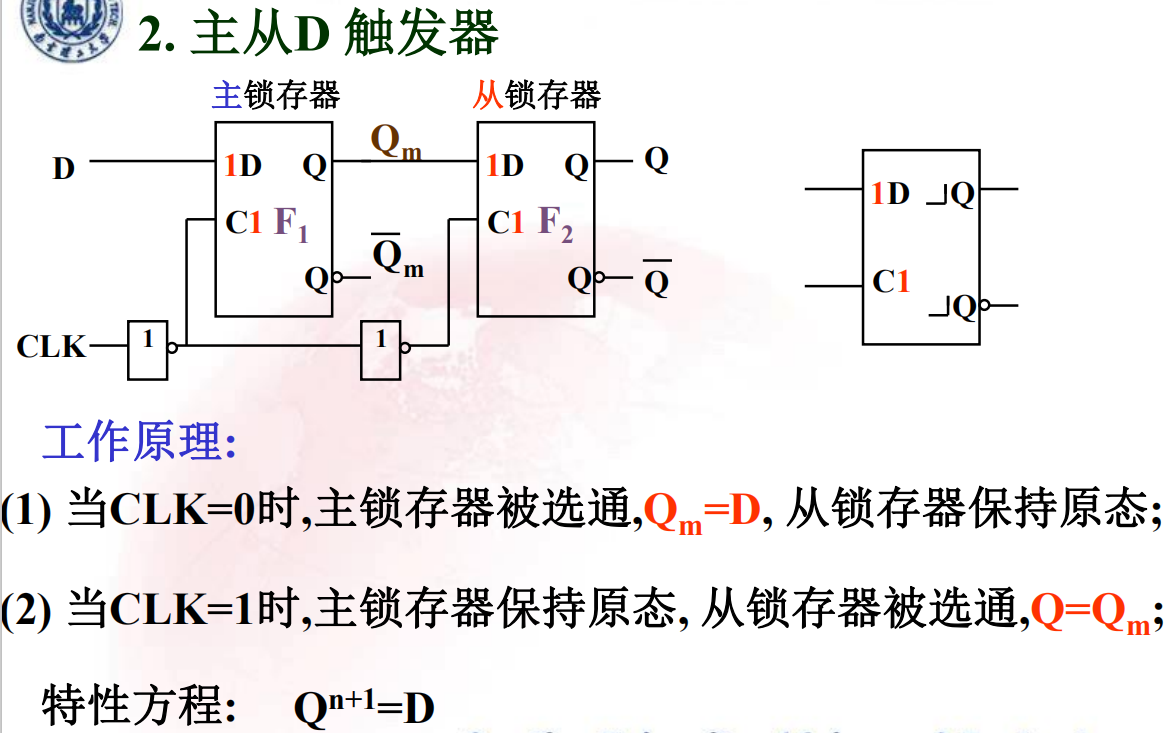

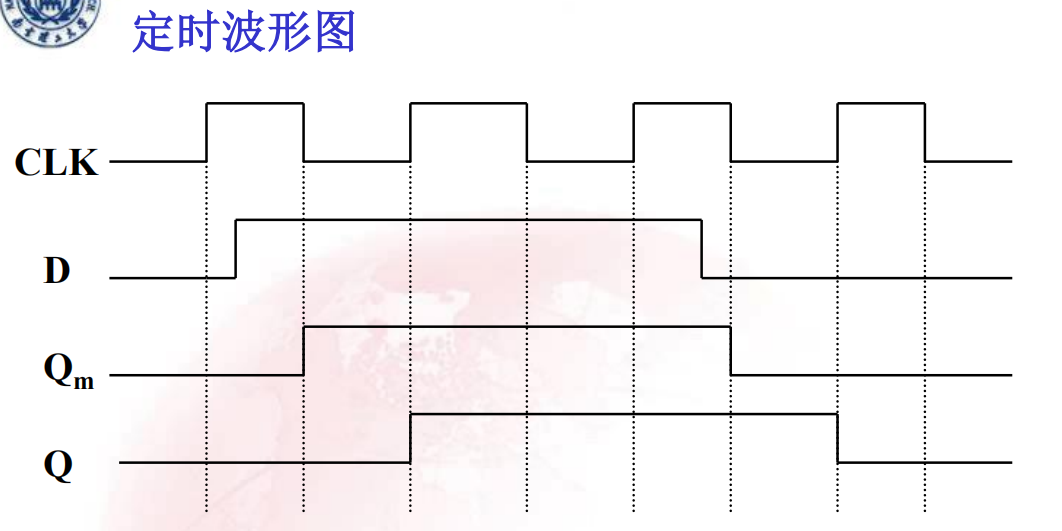

主从D触发器

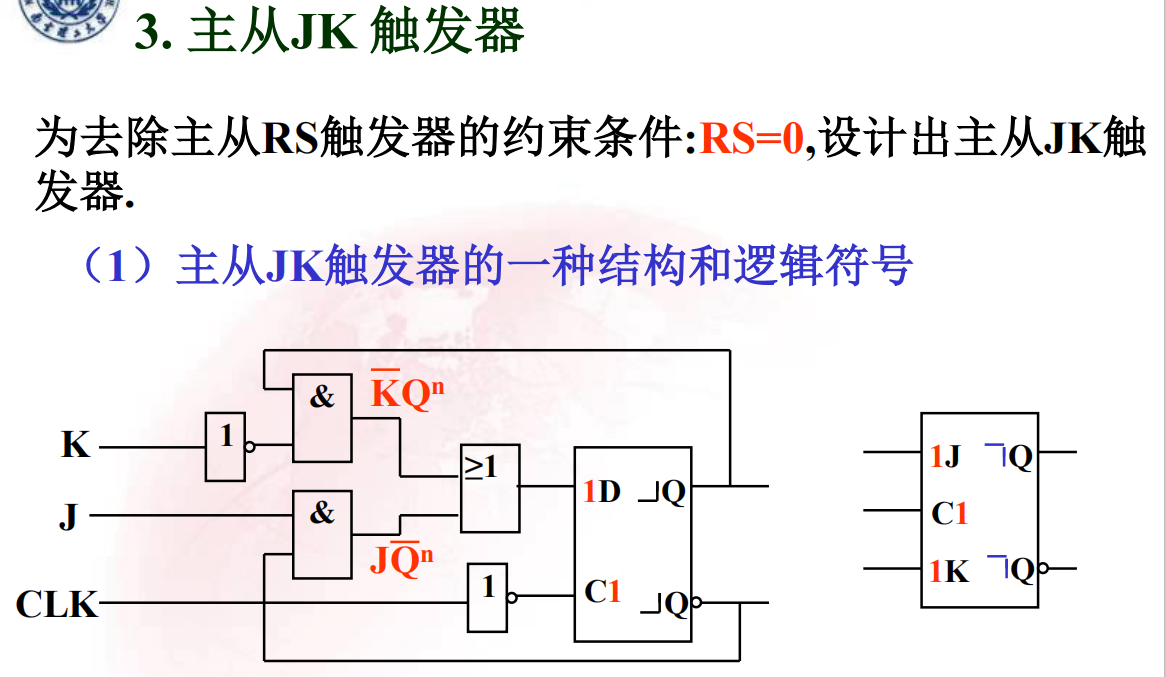

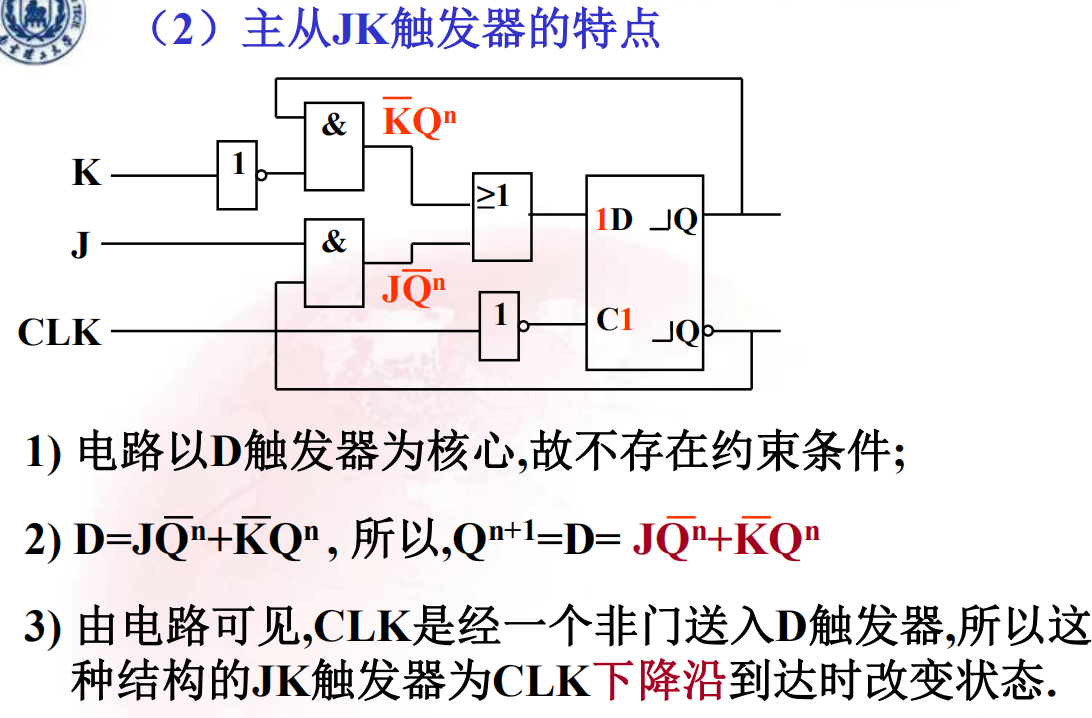

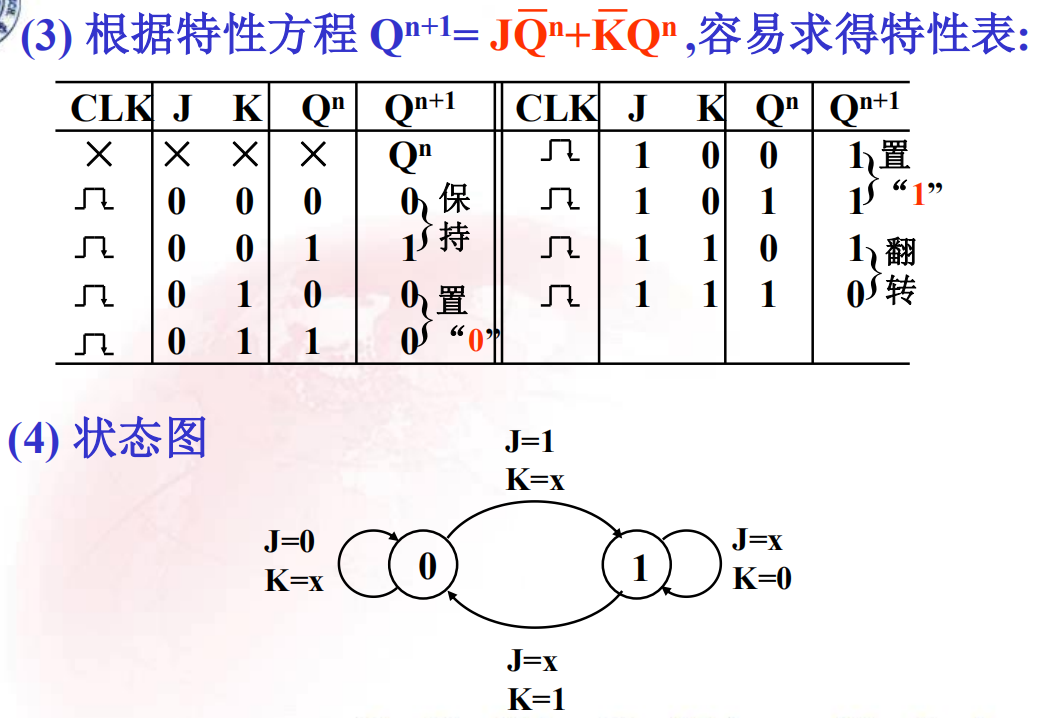

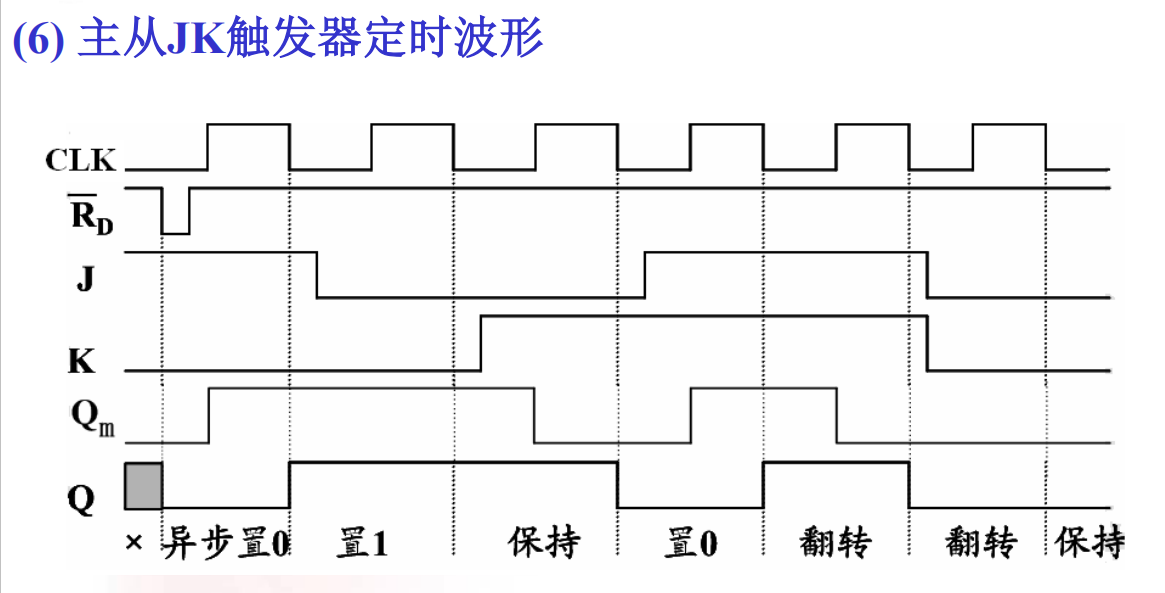

主从JK触发器

主从JK触发器其实就是将RS触发器中的RS = 0 的约束条件给解除。当R = S = 1时,主从JK触发器将状态值进行翻转。

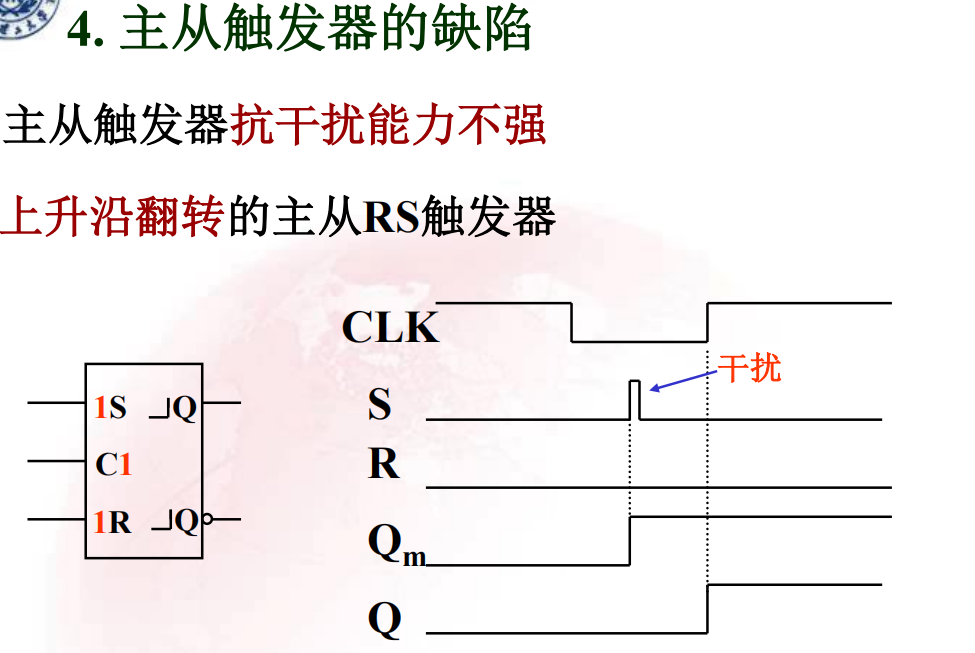

主从触发器的缺陷

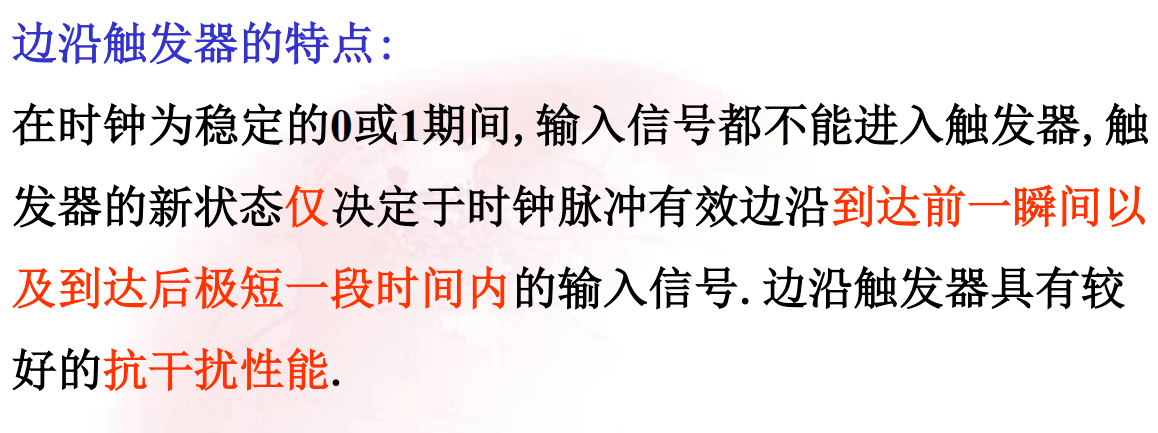

边沿触发器

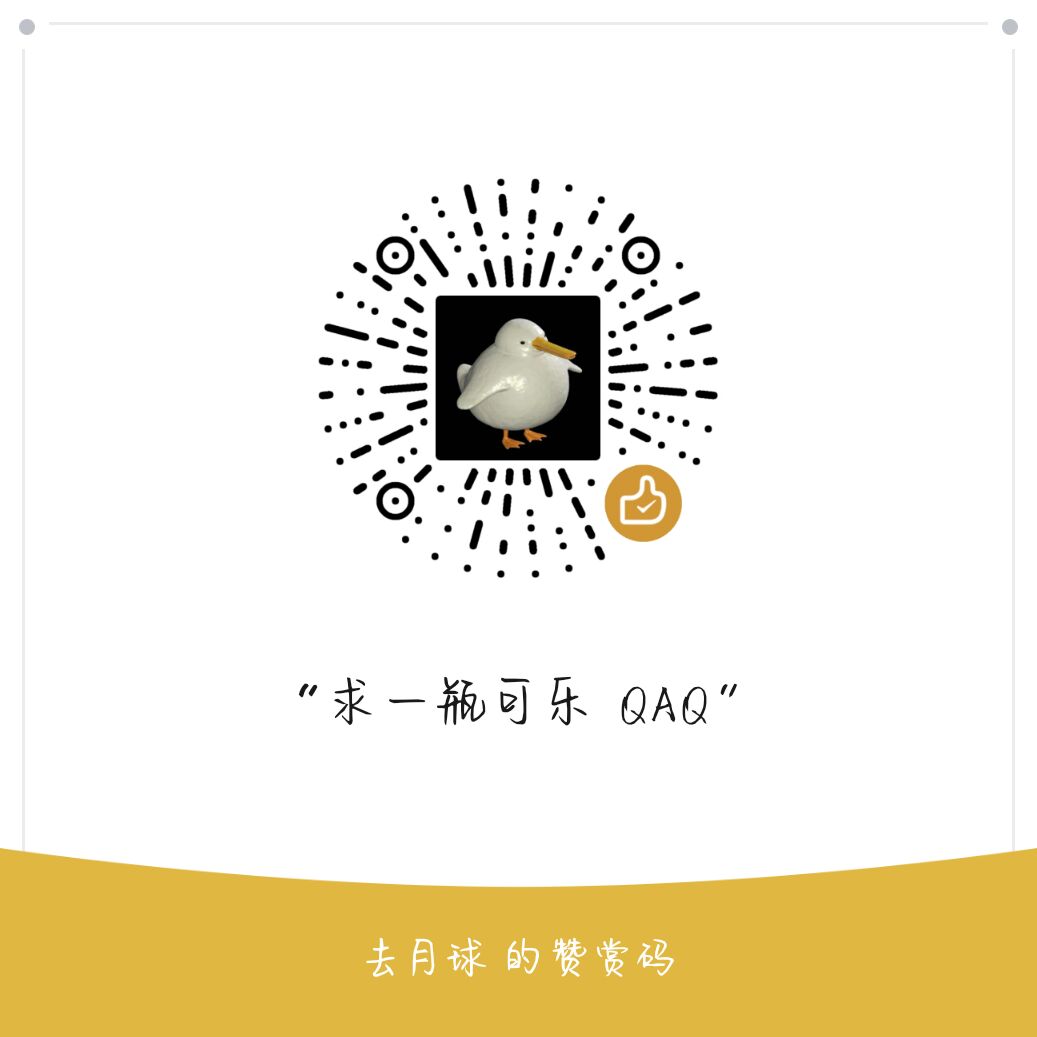

同步时序电路

由于在同步时序电路中,各触发器的动作变化是在CLK脉冲作用下同时发生的,因此,在同步电路的分析中,只要知道了在当前状态下各触发器的输入(即驱动信号),就能根据触发器的特性方程,求得电路的下一个状态,最终找到电路的状态转换规律。

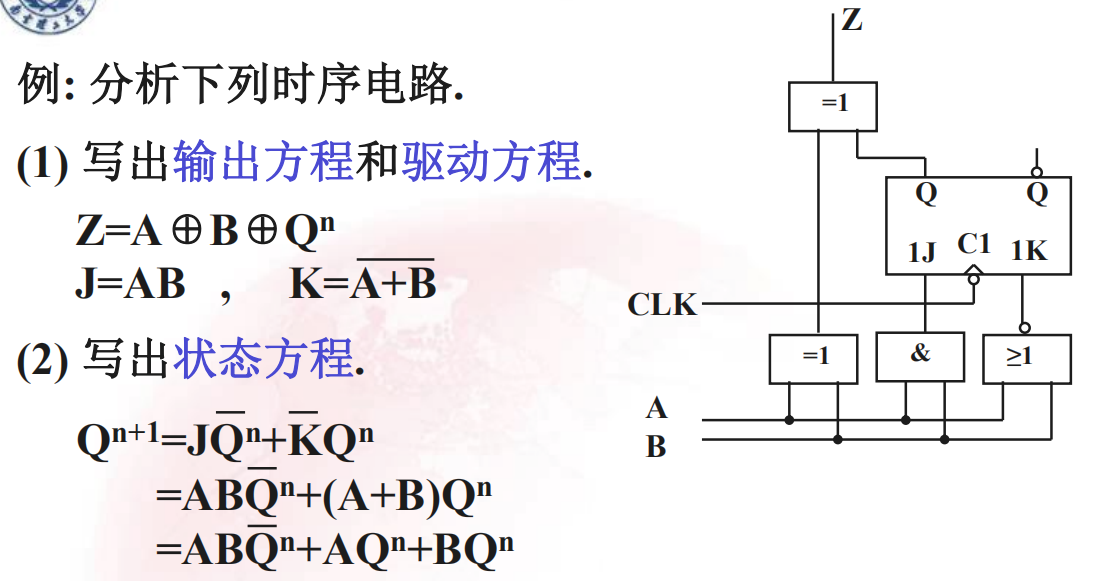

image-20211225212640852 image-20211225212654631

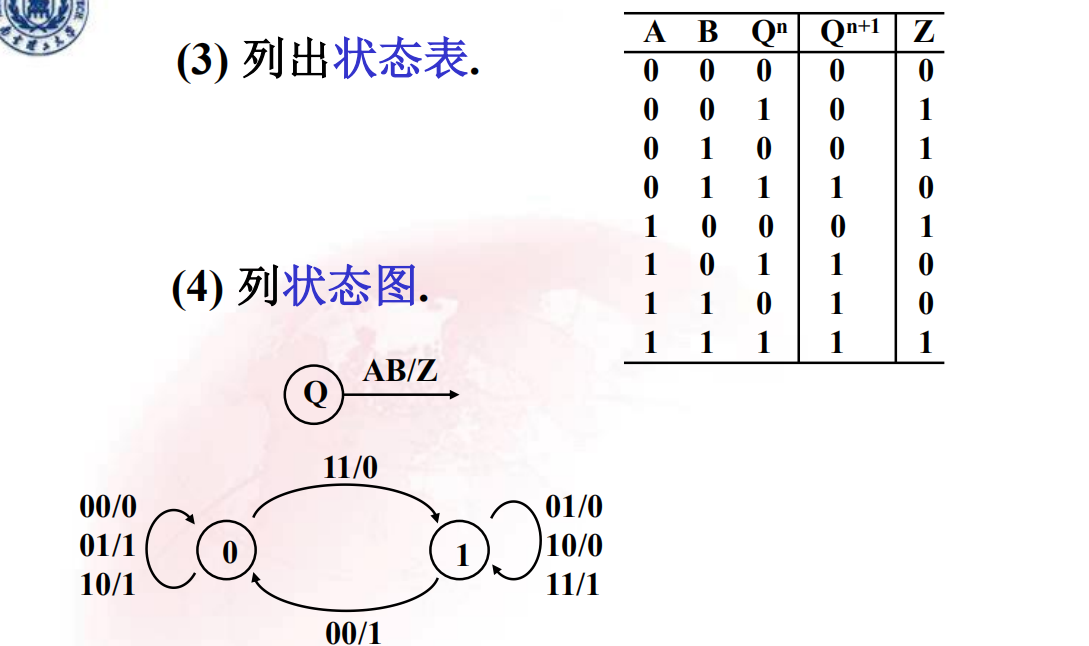

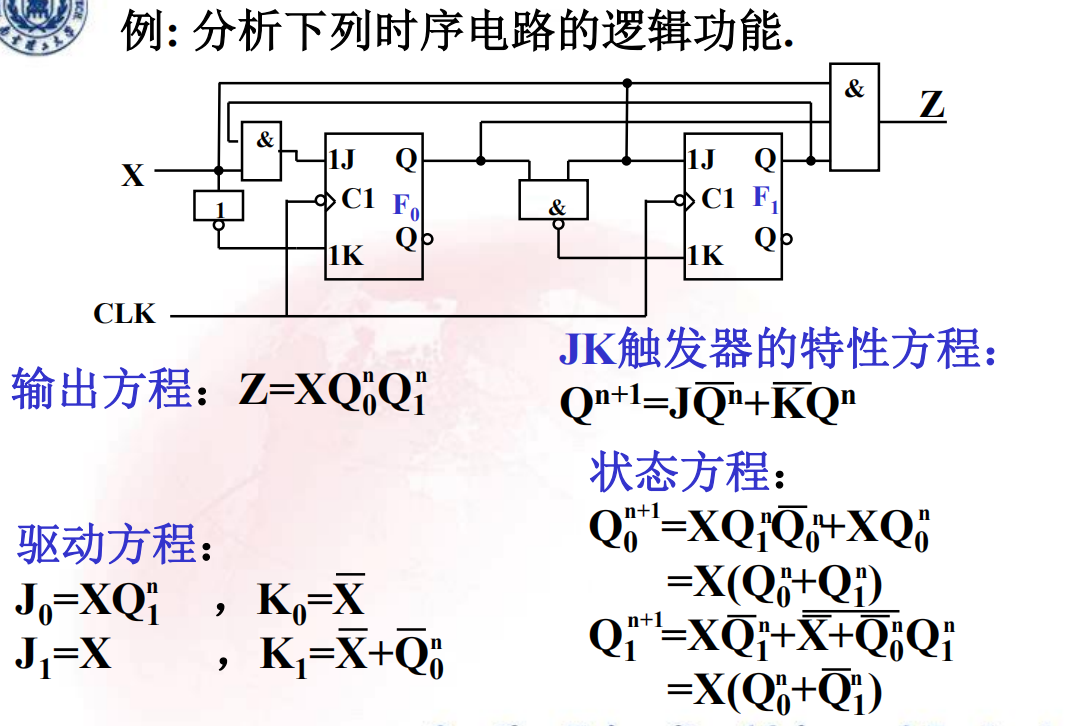

image-20211225212741877 image-20211225212756171

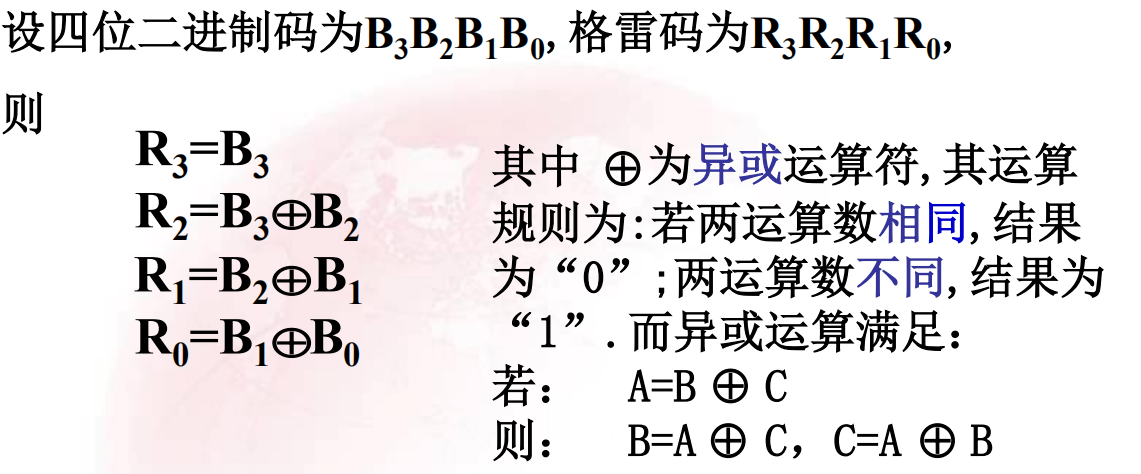

第六章 常用时序逻辑功能器件

第六章就一句话

数字逻辑复习